# **Digital Cellular Systems**

by

#### Dr. P. V. Ramana,

Professor & Head, Dept. of ECE, Sree Vidyanikethan Engineering College, Tirupati

Unit: V Course: Cellular & Mobile Communications Target Group: IV B.Tech. ECE

# Outline

- GSM-Introduction

- Architecture

- Frame Structure

- Channels

# What is GSM ?

Global System for Mobile Communication (GSM) is a second generation cellular standard developed to cater voice services and data delivery using digital modulation

# **GSM: History**

- Developed by Group Special Mobile (founded 1982) which was an initiative of CEPT ( Conference of European Post and Telecommunication )

- Aim : to replace the incompatible analog system

- Presently the responsibility of GSM standardization resides with special mobile group under ETSI (European telecommunication Standards Institute)

- Full set of specifications phase-I became available in 1990

- Under ETSI, GSM is named as Global System for Mobile communication

- Today many providers all over the world use GSM (more than 135 countries in Asia, Africa, Europe, Australia, America)

- More than 1300 million subscribers in world and 45 million subscriber in India.

# **GSM Services**

- Tele-services

- Bearer or Data Services

- Supplementary services

# **Tele Services**

- Telecommunication services that enable voice communication

- via mobile phones

- Offered services

- Mobile telephony

- Emergency calling

# **Bearer Services**

- Include various data services for information transfer between GSM and other networks like PSTN, ISDN etc at rates from 300 to 9600 bps

- Short Message Service (SMS)

-up to 160 character alphanumeric data transmission to/from the mobile terminal

- Unified Messaging Services(UMS)

- Group 3 fax

- Voice mailbox

- Electronic mail

# **Supplementary Services**

#### **Call related services :**

- Call Waiting- Notification of an incoming call while on the handset

- Call Hold- Put a caller on hold to take another call

- Call Barring- All calls, outgoing calls, or incoming calls

- Call Forwarding- Calls can be sent to various numbers defined by the user

- Multi Party Call Conferencing Link multiple calls together

- CLIP Caller line identification presentation

- CLIR Caller line identification restriction

- CUG Closed user group

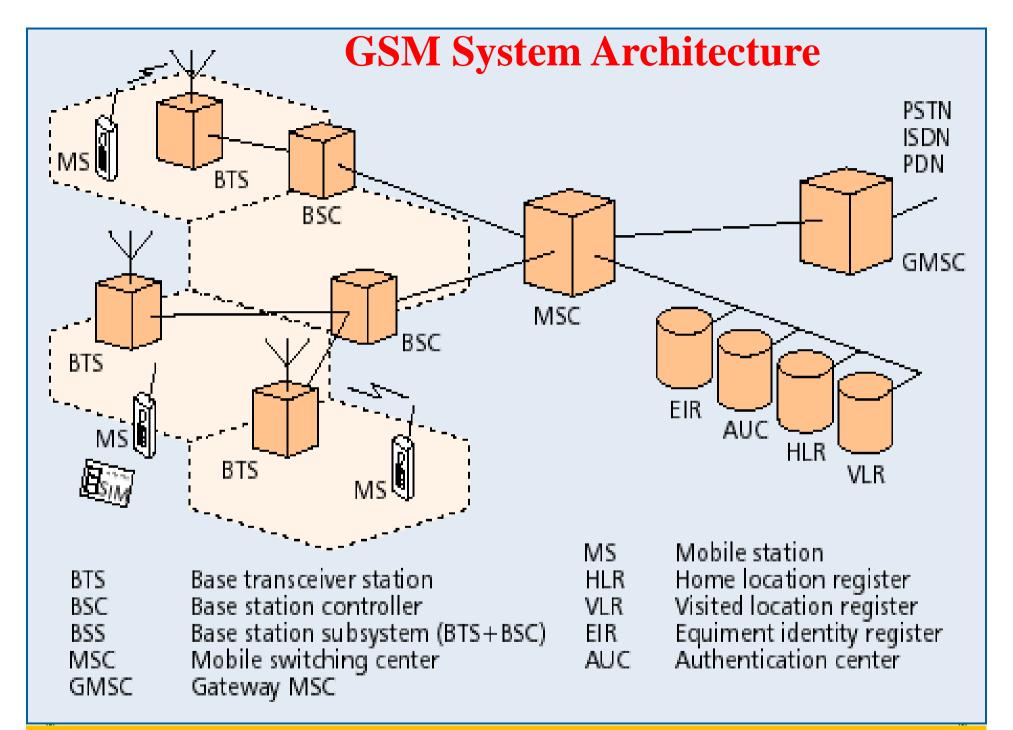

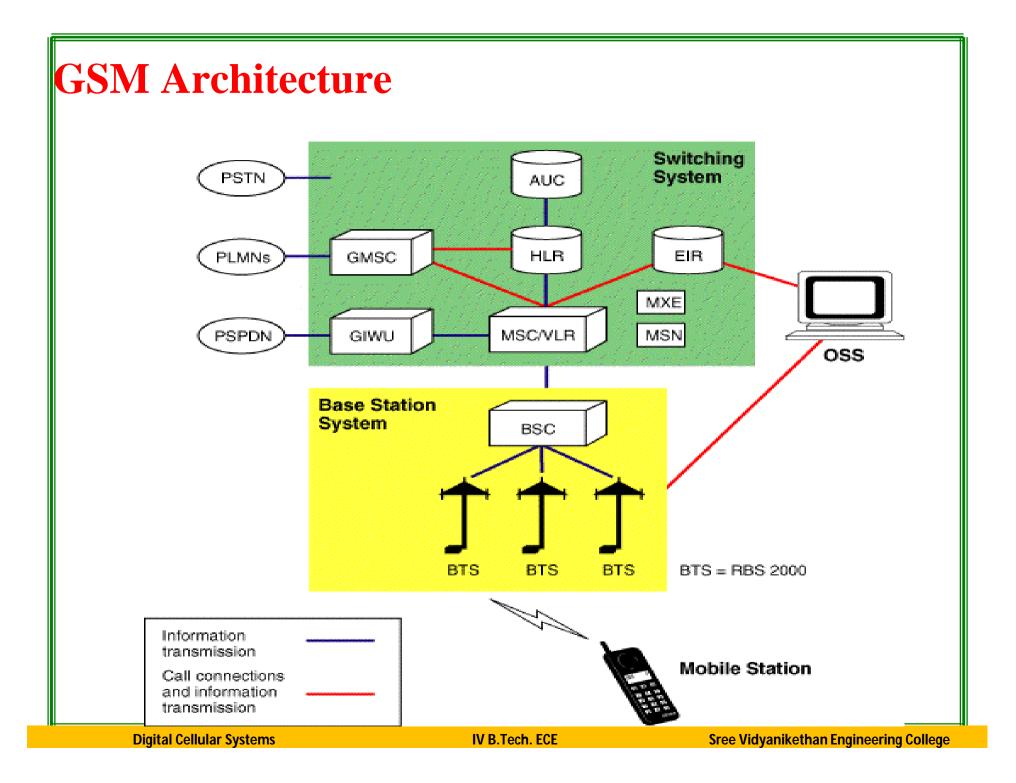

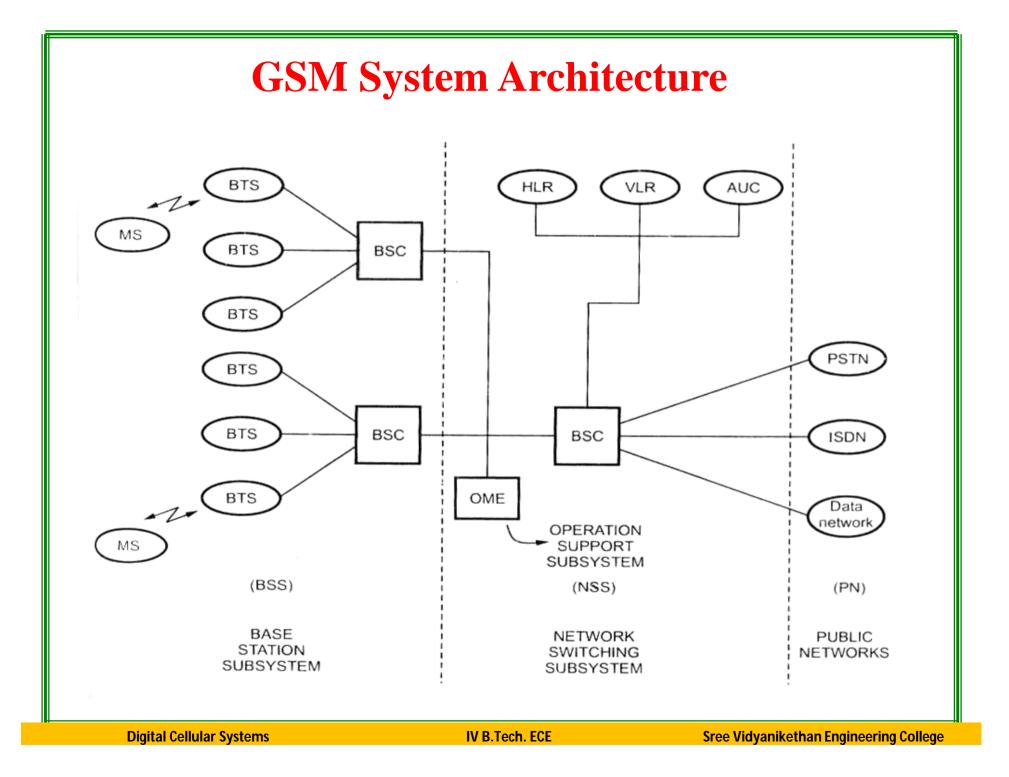

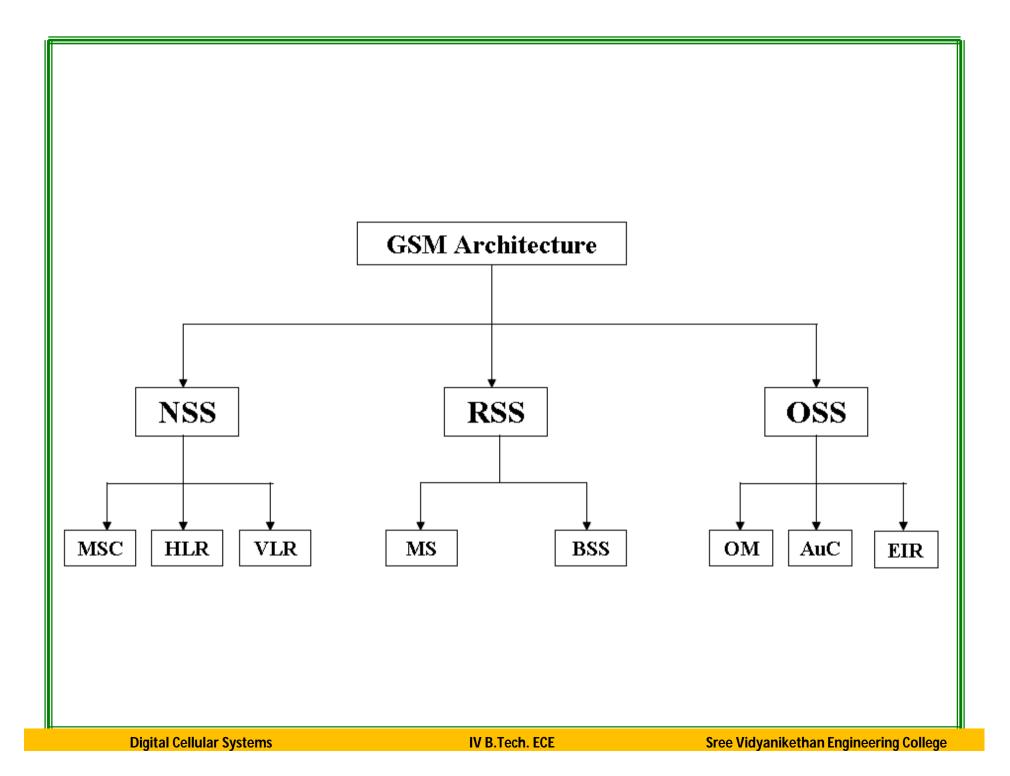

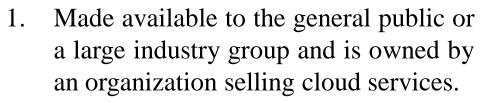

In GSM architecture, the subsystems are

Network and Switching Subsystems (NSS)

Radio Subsystem (RSS)

Operational Subsystems (OSS)

# **Network and Switching Subsystem (NSS)**

- It manages the connectivity between wireless N/Ws and public N/Ws. It consists of

- > Mobile Switching Center (MSC)-central administration and cellular co-ordination

- Home Location Register (HLR)- maintaining home user profile

- Visitor Location Register (VLR)- maintaining visitors/new user profile

#### Mobile Switching Center (MSC)

- Heart of the network

- Manages communication between GSM and other networks

- Call setup function and basic switching

- Call routing

- Billing information and collection

- Mobility management

- Registration

- Location Updating

- Inter BSS and inter MSC call handoff

- MSC does gateway function while its customer roams to other network by using HLR/VLR.

#### Home Location Registers (HLR)

- Permanent database about mobile subscribers in a large service area(generally one per GSM network operator)

- Database contains IMSI,MSISDN,prepaid/postpaid,roaming restrictions,supplementary services.

#### Visitor Location Registers (VLR)

- Temporary database which updates whenever new MS enters its area, by HLR database

- Controls those mobiles roaming in its area

- Reduces number of queries to HLR

- Database contains IMSI,TMSI,MSISDN,MSRN,Location Area,authentication key

# **Radio Subsystem**

- It consists of two main parts

- Mobile Station

- Base Station System

#### The Mobile Station is made up of two entities:

- 1. Mobile Equipment (ME)

- 2. Subscriber Identity Module (SIM)

#### **1. Mobile Equipment**

- Portable, vehicle mounted, hand held device

- Uniquely identified by an IMEI (International Mobile Equipment Identity)

- Voice and data transmission

- Monitoring power and signal quality of surrounding cells for optimum handover

- Power level : 0.8W 20 W

- 160 character long SMS.

Digital Cellular Systems

IV B.Tech. ECE

### 2. Subscriber Identity Module (SIM)

- Smart card contains the International Mobile Subscriber Identity (IMSI)

- Allows user to send and receive calls and receive other subscribed services

- Encoded network identification details

- Protected by a password or PIN

- Can be moved from phone to phone contains key information to activate the phone

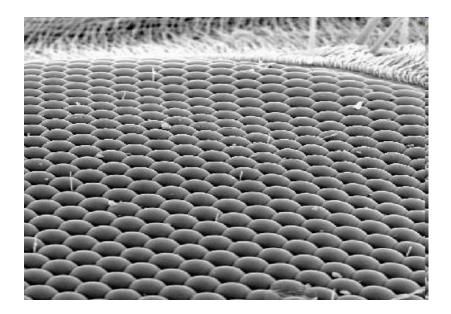

### **Base Station Subsystem (BSS)**

Base Station Subsystem is composed of two parts

- 1. Base Transceiver Station (**BTS**)

- 2. Base Station Controller (**BSC**)

#### **1. Base Transceiver Station (BTS):**

- Encodes, encrypts, multiplexes, modulates and feeds the RF signals to the antenna.

- Frequency hopping

- Communicates with Mobile station and BSC

- Consists of Transceivers (TRX) units

#### 2. Base Station Controller (BSC)

- Manages Radio resources for BTS

- Assigns Frequency and time slots for all MS's in its area

- Handles call set up

- Transcoding and rate adaptation functionality

- Handover for each MS

- Radio Power control

- It communicates with MSC and BTS

### **Operation and maintenance Subsystem (OSS)**

### Base Station Subsystem is composed of two parts

- 1. Operation and Maintenance (OM)

- 2. Authentication Centre (Au C)

- 3. Equipment Identity Register (EIR)

#### 2. Authentication Center (Au C)

- Protects against intruders in air interface

- Maintains authentication keys and algorithms and provides security triplets

- Generally associated with HLR

#### **3. Equipment Identity Register (EIR)**

- Database that is used to track handsets using the IMEI

- Made up of three sub-classes: The White List, The Black List and the Gray List

- Only one EIR per PLMN

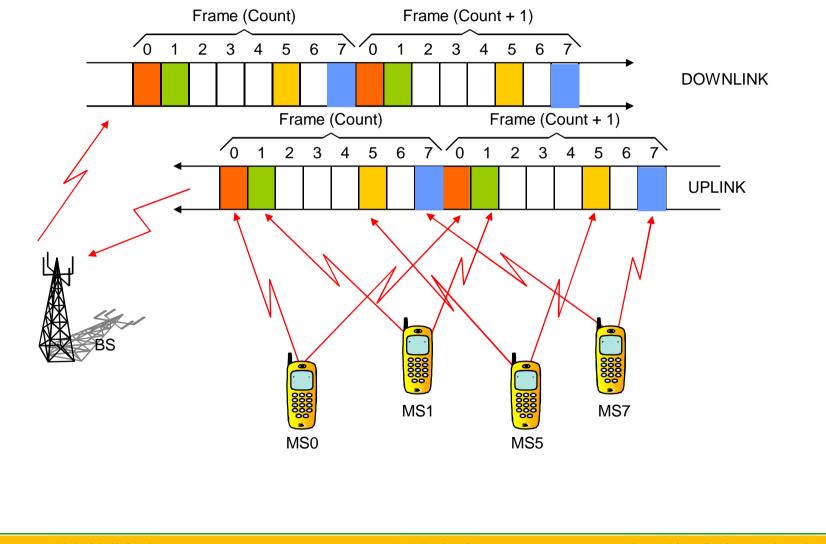

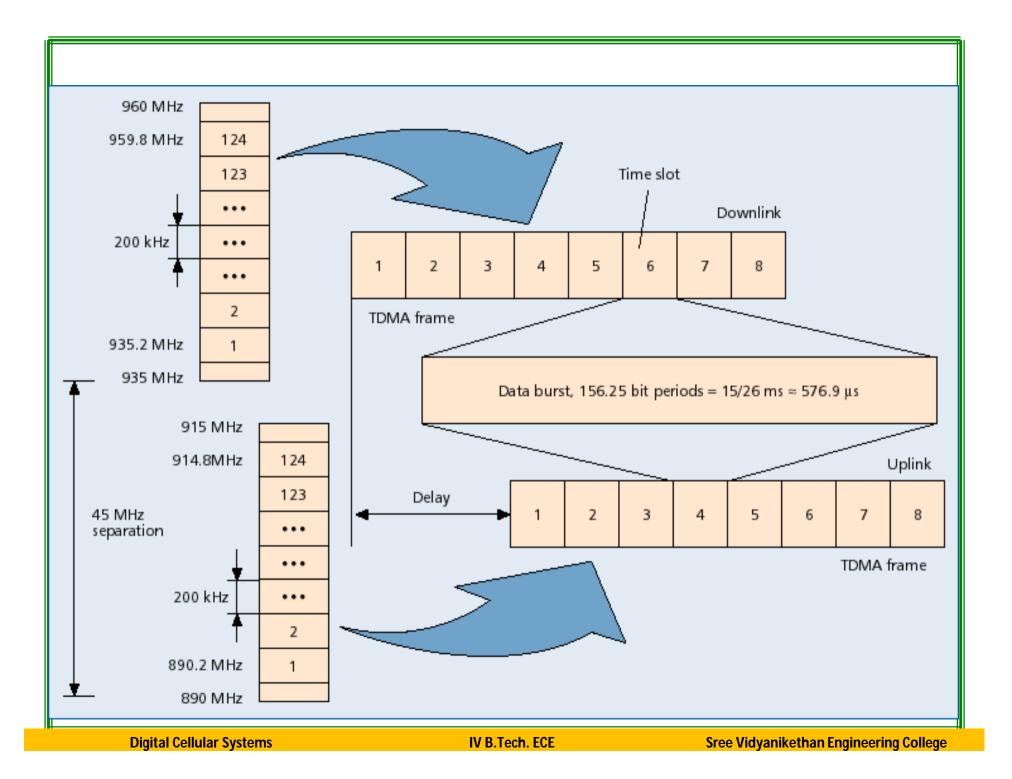

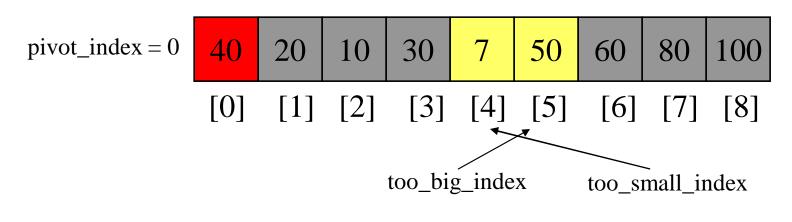

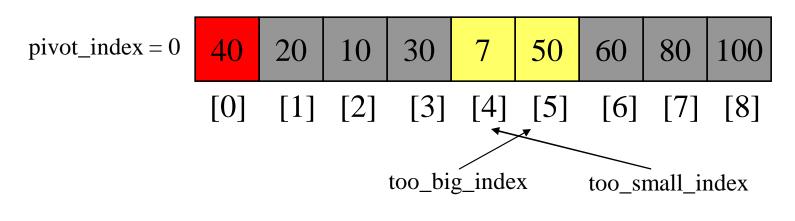

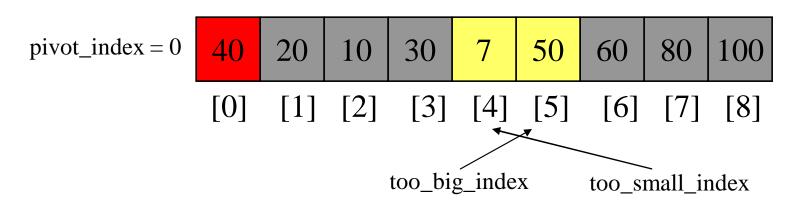

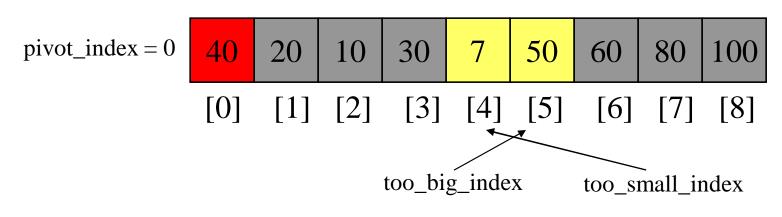

# TDMA Operation in GSM

Full Rate

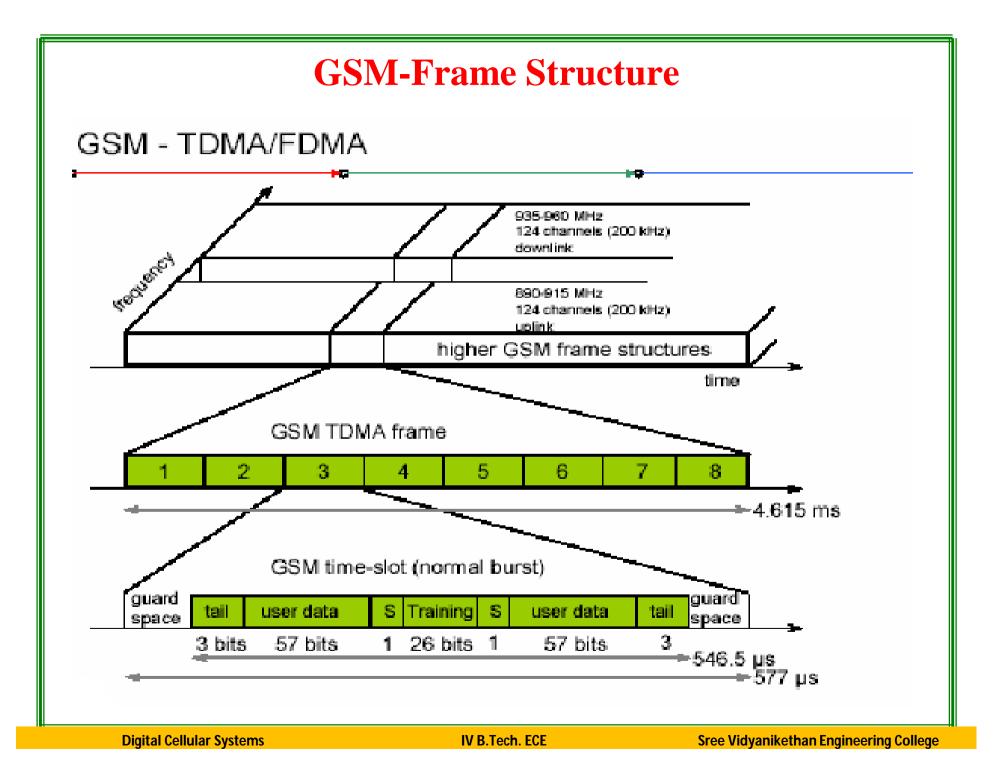

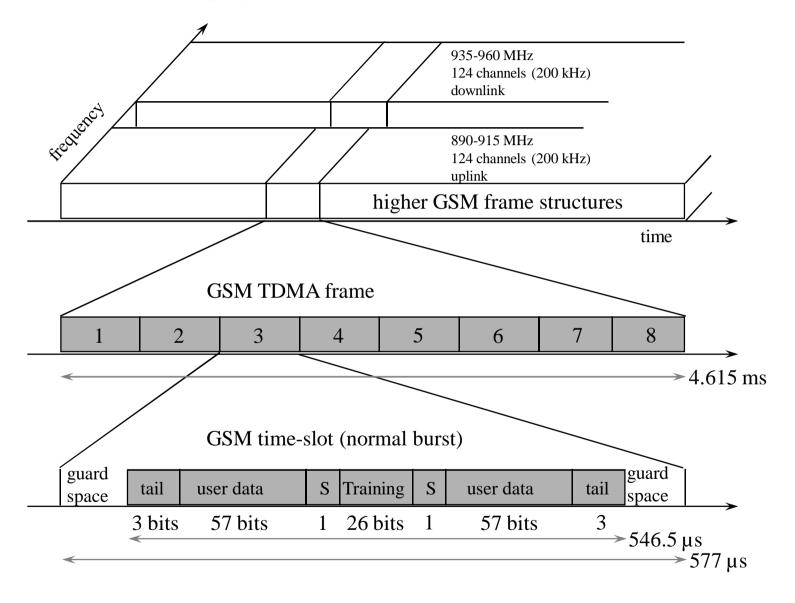

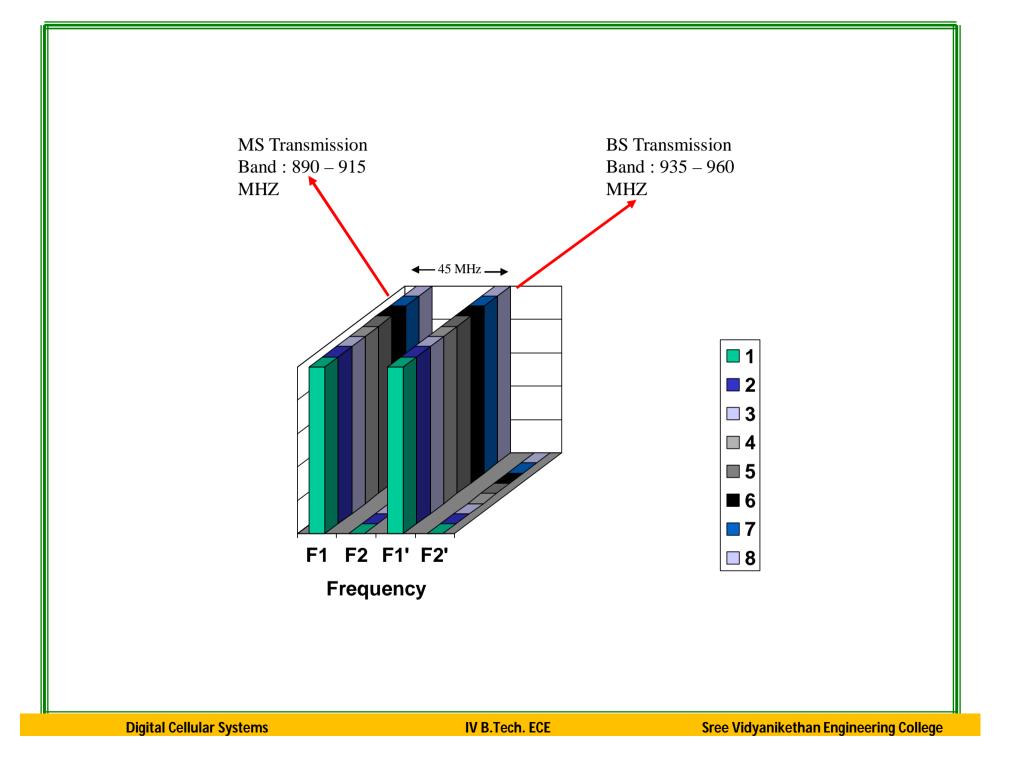

# GSM - TDMA/FDMA

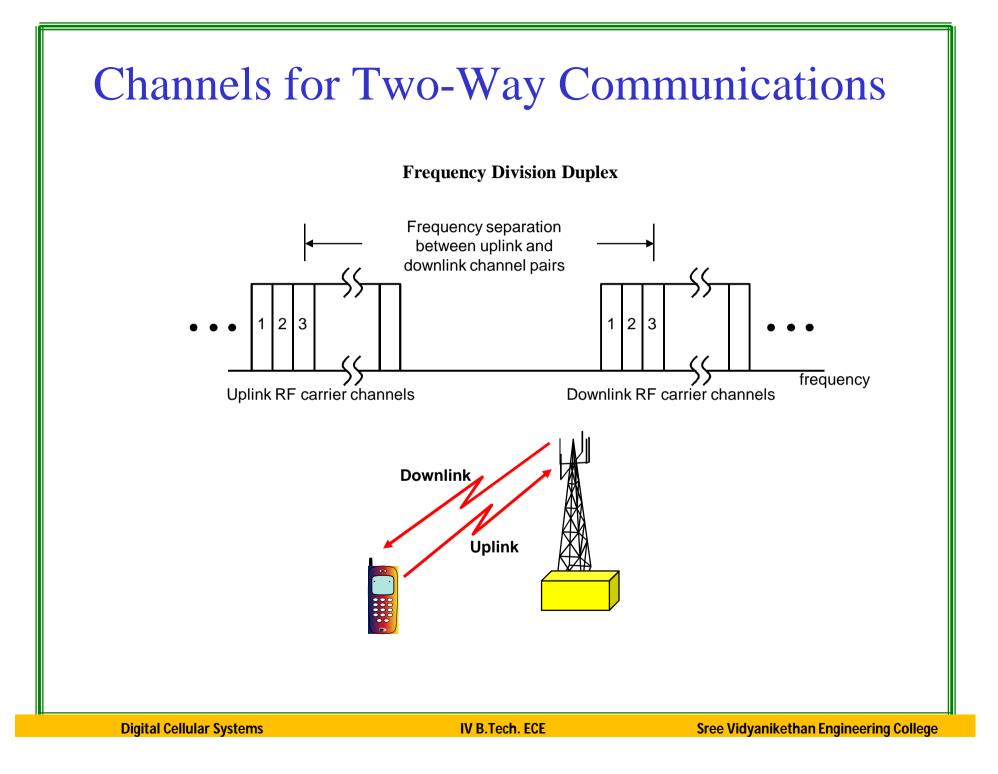

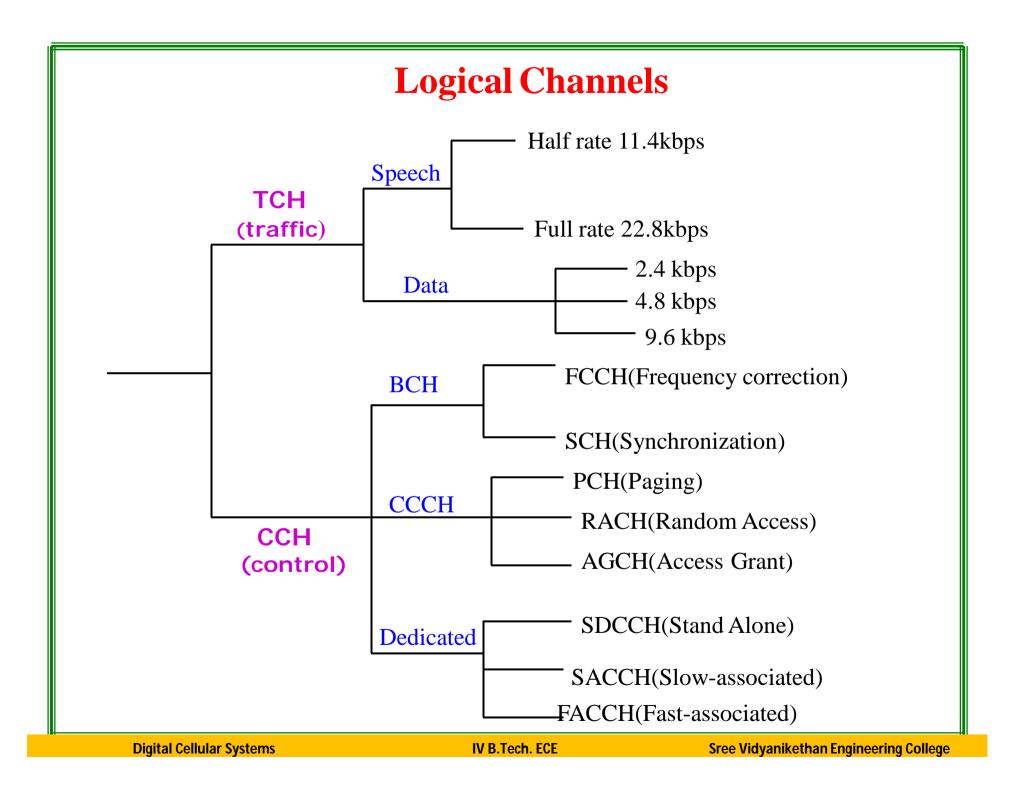

#### **Logical Channels**

#### • Traffic Channels (TCH)

- TCH/F and TCH/H for full and half rate speech channels.

- TCH/9.6, TCH/4.8 and TCH/2.4 for 9.6, 4.8 and 2.4 kb/s data channels.

#### • Broadcast Channels (BCH)

- Frequency Correction Channel (FCCH),

- Synchronization Channel (SCH),

- Broadcast Control Channel (BCCH).

#### Common control channels

- Paging Channel (PCH),

- Access Grant Channel (AGCH),

- Random Access Channel (RACH).

#### Dedicated control channels

- Stand-alone Dedicated Control Channel (SDCCH),

- Slow Associated Control Channel (SACCH),

- Fast Associated Control Channel (FACCH).

# Number of channels in GSM

- Freq. Carrier: 200 kHz

- TDMA: 8 time slots per freq carrier

- No. of carriers = 25 MHz / 200 kHz = 125

- Max no. of user channels = 125 \* 8 = 1000

- Considering guard bands = 124 \* 8 = 992 channels

#### **Air Interface: Logical Channel**

- Traffic Channel (TCH)

- Carries user voice traffic

- Signalling Channel

- Broadcast Channel (BCH) (unidirectional)

- Common Control Channel (CCH) (unidirectional)

- Dedicated/Associated Control Channel (DCCH/ACCH) (bidirectional)

### BCCH

- Broadcast Control Channel (BCCH)

- BTS to MS

- send cell identities, organization info about common control channels, cell service available, etc

#### Radio channel configuration

– Current cell + Neighbouring cells

#### Synchronizing information

– Frequencies + frame numbering

#### Registration Identifiers

- LA + Cell Identification (CI) + Base Station Identity Code (BSIC)

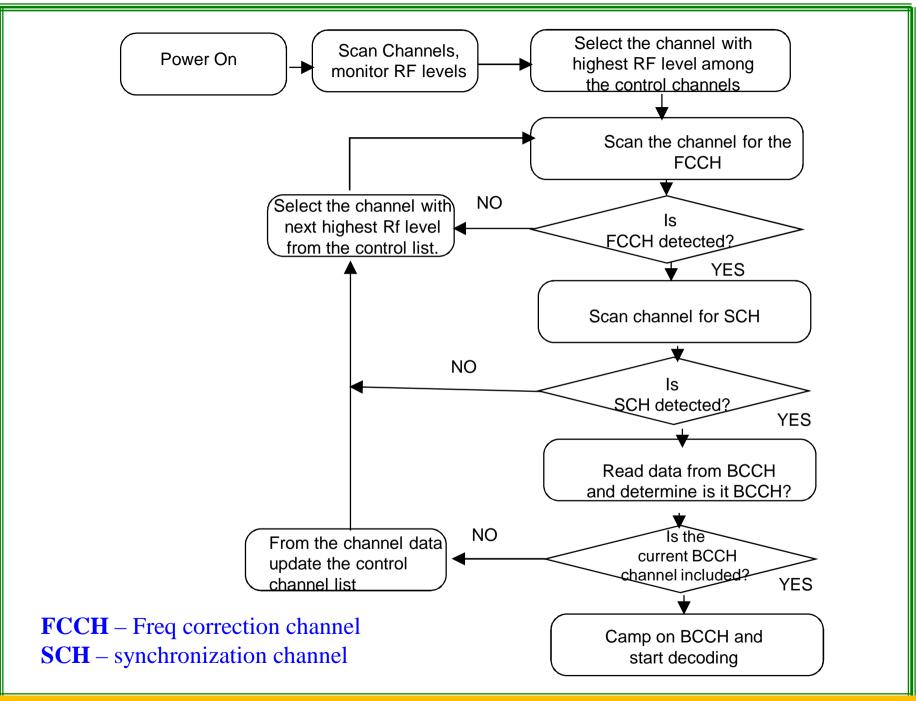

# FCCH & SCH

#### Frequency Correction Channel

- send a frequency correction data burst containing all zeros to effect a constant frequency shift of RF carrier

- Mobile station knows which frequency to use

- Repeated broadcast of Frequency Bursts

#### Synchronization Channel

- send TDMA frame no. and base station identity code to synchronize MSs

- MS knows which timeslot to use

- Repeated broadcast of Synchronization Bursts

### AGCH & PCH

- Access Grant Channel (AGCH)

- BTS to MS

- Used to assign an SDCCH/TCH to MS

- Paging Channel (PCH)

- BTS to MS

- Page MS

### **RACH & SDCCH**

#### Random Access Channel (RACH)

- $\checkmark MS => BTS$

- ✓ Slotted Aloha

- Request for dedicated SDCCH

- **Standalone Dedicated Control Channel (SDCCH)**

- $\checkmark MS => BTS$

- ✓ Standalone; Independent of Traffic Channel

- ✓ Used before MS is assigned a TCH

# DCCH

#### **DCCH (dedicated control channel):**

- Bidirectional point-to-point main signaling channels

- SDCCH (stand-alone dedicated control channel):

- SACCH (slow associated control channel): for out-of-band signaling associated with a traffic channel, eg.: signal strength measurements.

- FACCH (fast associated control channel): for preemptive signaling on a traffic channel, eg, for handoff messages Uses timeslots which are otherwise used by the TCH`

## **GSM: Frequency Hopping**

- Optionally, TDMA is combined with frequency hopping to address problem of channel fading

- TDMA bursts are transmitted in a pre-calculated sequence of different frequencies (algorithm programmed in mobile station)

- If a TDMA burst happens to be in a deep fade, then next burst most probably will not be so

- Helps to make transmission quality more uniform among all subscribers

### **Bursts**

Building unit of physical channel

Types of bursts

**Normal:** for transmitting messages in traffic and control channels **Frequency Correction:** sent by base station for frequency correction at mobile station

Synchronization: sent by base station for synchronization

Access: for call setup

**Dummy:** to fill an empty timeslot in the absence of data

### **Traffic Channel**

- Transfer either encoded speech or user data

- Bidirectional

- Full Rate TCH

- Rate 22.4kbps

- Half Rate TCH

- Rate 11.2 kbps

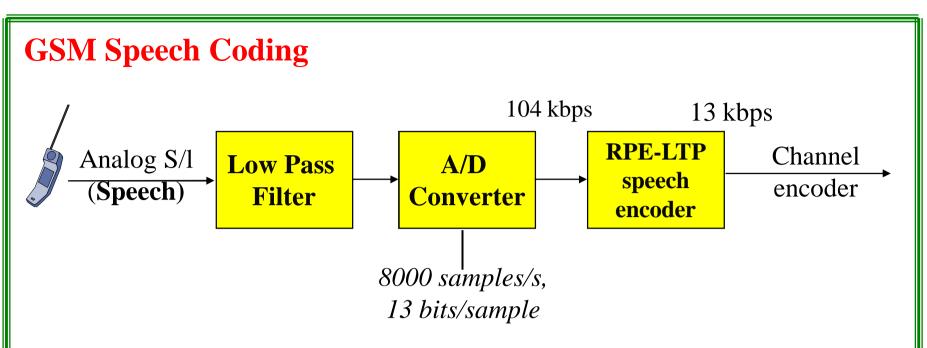

### **Full Rate Speech Coding**

- Speech Coding for 20ms segments

- 260 bits at the output ; Effective data rate 13kbps

- Unequal error protection

- 182 bits are protected

- 78 bits unprotected

- Channel Encoding

- Codes 260 bits into (8 x 57 bit blocks) 456 bits

- Interleaving

- 2 blocks of different set interleaved on a normal burst (save damages by error bursts)

#### **SACCH & FACCH**

- **Slow Associated Control Channel (SACCH)**

- Always associated with either TCH or SDCCH

- Information

- Channel quality, signal power level

- Should always be active; as proof of existence of physical radio connection

- Fast Associated Control Channel (FACCH)

- Handover

- Uses timeslots which are otherwise used by TCH (Pre-emptive multiplexing on a TCH, Stealing Flag (SF))

#### **GSM: Channel Summary**

- Logical channels

- ✓ Traffic Channels; Control Channels

- Physical Channel

✓ Time Slot Number; TDMA frame; RF Channel Sequence

- Mapping in frequency

- ✓ 124 channels, 200KHz spacing

- Mapping in time

✓ TDMA Frame, Multi Frame, Super Frame, Channel

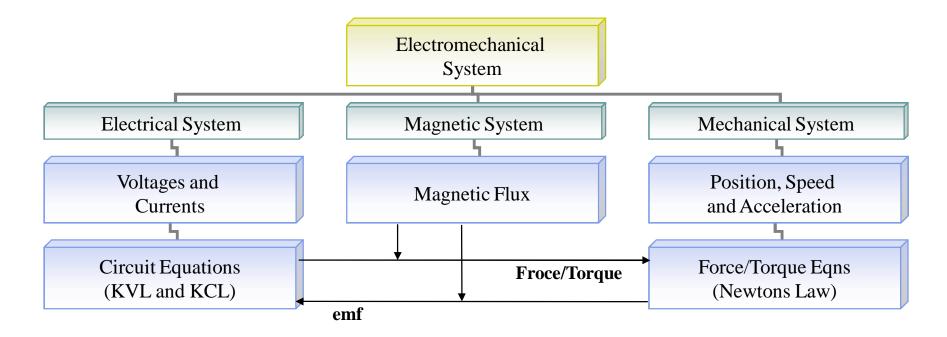

# Electromechanical Energy Conversion

By Mr. M. Manohara Associate Professor, Dept. of EEE

Unit: I Course: **DC Machines** Target Group: **II B.Tech. I Sem EEE**

#### Introduction

Electromechanical energy conversions – use a magnetic field as the medium of energy conversion

Electromechanical energy conversion device:

Converts electrical energy into mechanical energy

or

Converts mechanical energy into electrical energy.

#### Introduction

Three categories of electromechanical energy conversion devices:

- Transducers (for measurement and control)- small motion

Transform the signals of different forms. Examples: microphones, sensors and speakers.

- Force producing devices (translational force)- limited mechanical motion.

Produce forces mostly for linear motion drives, Example Actuators - relays, solenoids and electromagnets.

Continuous energy conversion equipment.

Operate in rotating mode. Examples: motors and generators.

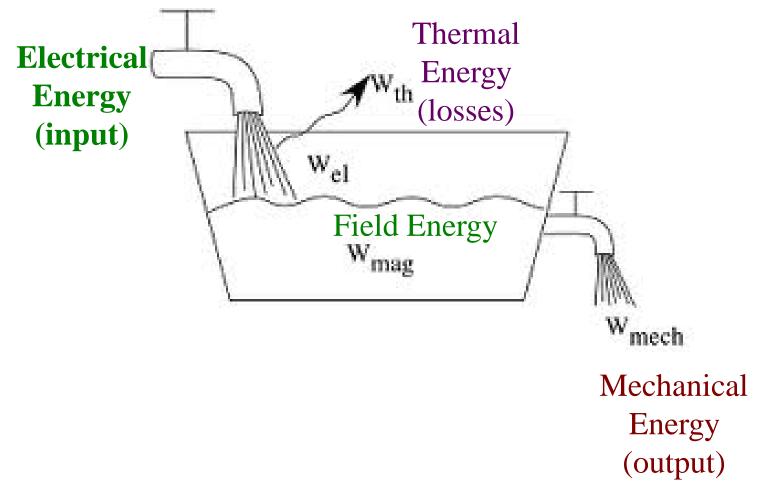

The principle of conservation of energy:

Energy can neither be created nor destroyed. It can only be changed from one form to another. Therefore total energy in a system is constant

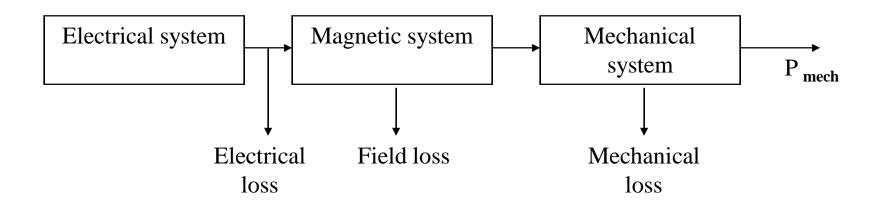

# An electromechanical converter system has three essential parts:

① An electrical system (electric circuits such as windings)

- 2 A magnetic system (magnetic field in the magnetic cores and air gaps)

- 3 A mechanical system (mechanically movable parts such as a rotor in an electrical machine).

# EM Energy Conversion: Analogy

Concept of electromechanical system modeling

The energy transfer equation is as follows:

7/18/2018

The energy balance can therefore be written as:

$\begin{pmatrix} Electrical \ energy \\ input \ from \ sources \\ -resis \tan ce \ loss \end{pmatrix} = \begin{pmatrix} Mechanical \ energy \\ output \ + friction \\ and \ windage \ loss \end{pmatrix} + \begin{pmatrix} Increase \ in \\ stored \ field \\ energy \ + core \ loss \end{pmatrix}$

For the lossless magnetic energy storage system in differential form,

#### $\mathbf{dW}_{\mathbf{e}} = \mathbf{dW}_{\mathbf{m}} + \mathbf{dW}_{\mathbf{f}}$

$dW_e = i d \lambda =$  differential change in electric energy input  $dW_m = f_m dx =$  differential change in mechanical energy output  $dW_f =$  differential change in magnetic stored energy

We can write

$$dW_e = ei dt; e = \frac{d\lambda}{dt}$$

$$dW_e = \frac{d\lambda}{dt}idt = id\lambda$$

- -

Here e is the voltage induced in the electric terminals by changing magnetic stored energy.

$$dW_e = ei dt = dW_m + dW_f$$

Together with Faraday's law for induced voltage, form the basis for the energy method.

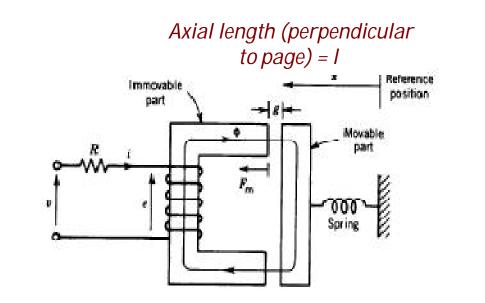

Singly-excited System

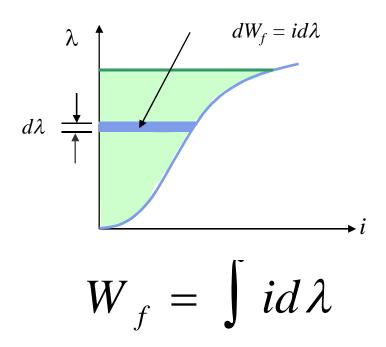

# Energy, Coenergy and Force or Torque

# Energy in Magnetic System

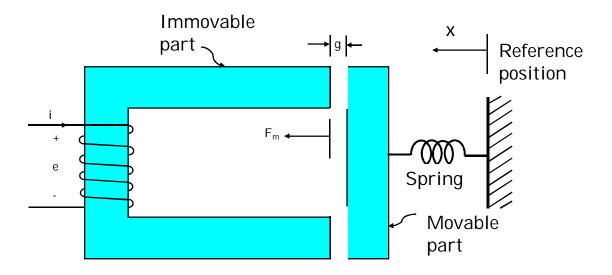

Consider the electromechanical system below:

Schematic of an electromagnetic relay

#### Energy in Magnetic System

The mechanical force  $f_m$  is defined as acting from the relay upon the external mechanical system and the differential mechanical energy output of the relay is

$$dW_m = f_m dx$$

Then, substitution  $dW_e = id \lambda$ , gives

$$dW_f = id \lambda - f_m dx$$

Value of  $W_f$  is uniquely specified by the values of  $\lambda$  and x, since the magnetic energy storage system is lossless.

#### **Energy in Magnetic System**

$dW_f$  = differential change in magnetic stored energy

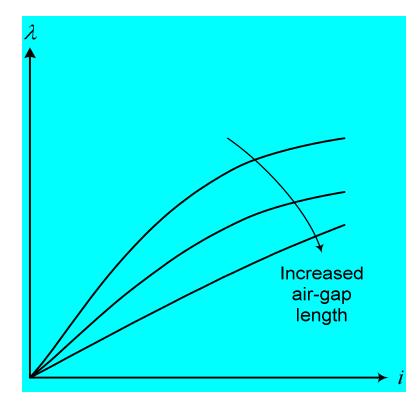

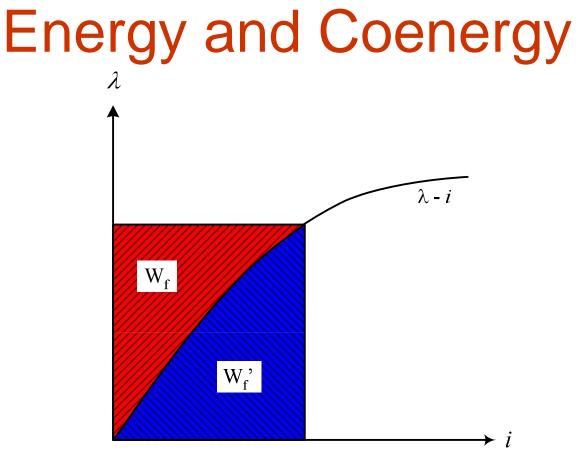

#### **Energy and Coenergy**

The  $\lambda$ -*i* characteristics of an electromagnetic system depends on the air-gap length and B-H characteristics of the magnetic material.

For a larger air-gap length the characteristic is essentially linear. The characteristic becomes non linear as the air-gap length decreases.

For a particular value of air-gap length, the <u>field energy</u> is represented by the red area between  $\lambda$  axis and  $\lambda$ -*i* characteristic. The blue area between *i* axis and  $\lambda$  - *i* characteristic is known as the <u>coenergy</u>

#### **Energy and Coenergy**

The coenergy is defined as  $W'_{f} = \int_{0}^{i} \lambda di$

From the figure of  $\lambda$  - *i* characteristic,

$W_{f}' + W_{f} = \lambda i$

Note that  $W_{f'} > W_{f}$  if the  $\lambda$  - *i* characteristic is non linear and  $W_{f'} = W_{f}$  if it is linear.

The quantity of coenergy has no physical significance. However, it can be used to derive expressions for force (torque) developed in an electromagnetic system

The magnetic stored energy  $W_f$  is a state function, determined uniquely by the independent state variables  $\lambda$  and x. This is shown explicitly by

$dW_f(\lambda, x) = id \lambda - f_m dx$

For any function of two independent variables  $F(x_1, x_2)$ , the total differential equation of F with respect to the two state variables  $x_1$  and  $x_2$  can be written

$$d\mathbf{F}(x_1, x_2) = \frac{\partial \mathbf{F}(x_1, x_2)}{\partial x_1} \bigg|_{x_2} dx_1 + \frac{\partial \mathbf{F}(x_1, x_2)}{\partial x_2} \bigg|_{x_1} dx_2$$

Therefore, for the total differential of  $W_f$

$$\mathrm{dW}_{\mathrm{f}}(\lambda, x) = \frac{\partial W_{\mathrm{f}}(\lambda, x)}{\partial \lambda} \bigg|_{x} d\lambda + \frac{\partial W_{\mathrm{f}}(\lambda, x)}{\partial x} \bigg|_{\lambda} dx$$

And we know that

$$\mathrm{dW}_{\mathrm{f}}(\lambda, x) = id\lambda - f_m dx$$

By matching both equations, the current:

$$i = \frac{\partial W_{f}(\lambda, x)}{\partial \lambda} \bigg|_{x}$$

where the partial derivative is taken while holding x constant and the mechanical force:

$$f_m = -\frac{\partial W_f(\lambda, x)}{\partial x} \bigg|_{\lambda}$$

where the partial derivative is taken while holding  $\lambda$  constant.

#### Determination of Force from Energy: Linear System

For a linear magnetic system for which  $\lambda = L(x)i$ :

$$W_{f}(\lambda, x) = \int_{0}^{\lambda} i(\lambda, x) d\lambda = \int_{0}^{\lambda} \frac{\lambda}{L(x)} d\lambda = \frac{1}{2} \frac{\lambda^{2}}{L(x)}$$

and the force,  $f_m$  can be found directly:

$$f_m = -\frac{\partial W_f(\lambda, x)}{\partial x} \bigg|_{\lambda} = -\frac{\partial}{\partial x} \left( \frac{1}{2} \frac{\lambda^2}{L(x)} \right) \bigg|_{\lambda} = \frac{\lambda^2}{2L(x)^2} \frac{dL(x)}{dx}$$

For a system with a rotating mechanical terminal, the mechanical terminal variables become the angular displacement θ and the torque *T*. Therefore, equation for the torque:

$$T = -\frac{\partial W_{f}(\lambda, \theta)}{\partial \theta} \bigg|_{\lambda}$$

where the partial derivative is taken while holding  $\lambda$  constant.

The coenergy  $W_f$  is defined as

$$W'_f(i,x) = i\lambda - W_f(\lambda,x)$$

and the differential coenergy  $dW_{f}$ :

$$dW'_f(i,x) = d(i\lambda) - dW_f(\lambda,x)$$

We know previously that

$$\mathrm{dW}_{\mathrm{f}}(\lambda, x) = id\lambda - f_m dx$$

7/18/2018

#### Determination of Force from Coenergy By expanding d(*i*λ):

$d(i\lambda) = id\lambda + \lambda di$

So, the differential coenergy  $dW_f$ :

$$dW'_{f}(i,x) = d(i\lambda) - dW_{f}(\lambda,x)$$

=  $id\lambda + \lambda di - (id\lambda - f_{m}dx)$

=  $\lambda di + f_{m}dx$

#### Determination of Force from Coenergy By expanding $dW_f(i,x)$ :

$dW'_{f}(i,x) = \frac{\partial W'_{f}(i,x)}{\partial i} \bigg|_{x} di + \frac{\partial W'_{f}(i,x)}{\partial x} \bigg|_{i} dx$

and, from the previous result:

$$dW'_f(i,x) = \lambda di + f_m dx$$

By matching both equations,  $\lambda$ :

$$\lambda = \frac{\partial W_{f}(i,x)}{\partial i} \bigg|_{x}$$

where the partial derivative is taken while holding x constant and the mechanical force:

$$f_{m} = \frac{\partial W_{f}(i,x)}{\partial x} \bigg|_{i}$$

where the partial derivative is taken while holding *i* constant.

#### Determination of Force from Coenergy: Linear System

For a linear magnetic system for which  $\lambda = L(x)i$ :

$$W'_{f}(i,x) = \int_{0}^{i} \lambda(i,x) di = \int_{0}^{i} L(x) i di = L(x) \frac{i^{2}}{2}$$

and the force,  $f_m$  can be found directly:

$$f_{m} = \frac{\partial W_{f}(i,x)}{\partial x} \bigg|_{i} = \frac{\partial}{\partial x} \left( L(x) \frac{i^{2}}{2} \right) \bigg|_{i} = \frac{i^{2}}{2} \frac{dL(x)}{dx}$$

## Determination of Torque from Coenergy

For a system with a rotating mechanical terminal, the mechanical terminal variables become the angular displacement θ and the torque *T*. Therefore, equation for the torque:

$$T = \frac{\partial W_{\rm f}(i,\theta)}{\partial \theta} \bigg|_{i}$$

where the partial derivative is taken while holding  $\lambda$  constant.

# Determination of Force Using Energy or Coenergy?

The selection of energy or coenergy as the function to find the force is purely a matter of convenience.

They both give the same result, but one or the other may be simpler analytically, depending on the desired result and characteristics of the system being analyzed.

#### **Direction of Force Developed**

1. By using energy function:  $f_m = -\frac{\partial W_f(\lambda, x)}{\partial x}$

The negative sign shows that the force acts in a direction to decrease the magnetic field stored energy at constant flux.

2. By using coenergy function:  $f_m = +\frac{\partial W_f(i,x)}{\partial x}$

The positive sign emphasizes that the force acts in a direction to increase the coenergy at constant current.

#### **Direction of Force Developed**

3. By using inductance function:

$$f_m = +\frac{i^2}{2} \frac{d\mathbf{L}(\mathbf{x})}{dx}\Big|_i$$

The positive sign emphasizes that the force acts in a direction to increase the inductance at constant current.

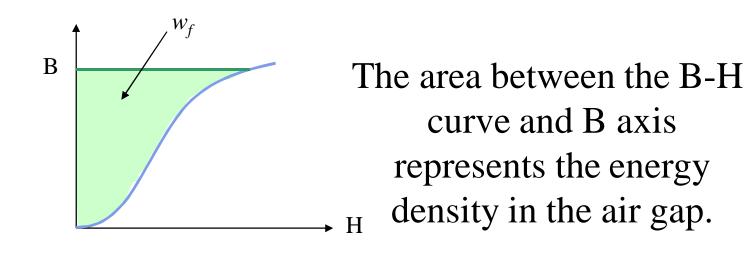

# **B-H Curve and Energy Density**

In a magnetic circuit having a substantial air gap g, and high permeability of the iron core, nearly all the stored energy resides in the gap. Therefore, in most of the cases we just need to consider the energy stored in the gap. The magnetic stored energy,

$$W_f = \int_0^\lambda i d\lambda$$

in which  $i = \frac{Hg}{N}$  and  $d\lambda = d(N\phi) = d(NAB) = NAdB$

\* Sen pg97

7/18/2018

Dr Awang Jusoh/Dr Makbul

#### **B-H Curve and Energy Density**

Therefore,

$$W_f = \int_0^B \frac{Hg}{N} NAdB = Ag \int_0^B HdB$$

However, Ag is volume of the air gap. Dividing both sides of the above equation by the volume Ag results in

$$w_f = \frac{W_f}{Ag} = \int_0^B H dB$$

\* Sen pg97

7/18/2018

Dr Awang Jusoh/Dr Makbul

## **B-H Curve and Energy Density**

where  $w_f = \int_0^B H dB$  is energy per unit volume  $w_f$  is known as energy density.

\* Sen pg97

Dr Awang Jusoh/Dr Makbul

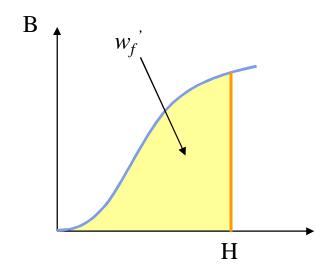

# **B-H Curve and Energy Density**

In the same manner,

$w'_f = \int_0^H BdH$  is coenergy per unit volume.

The area between the B-H curve and H axis represents the coenergy density in the air gap.

\* Sen pg97

Dr Awang Jusoh/Dr Makbul

# **B-H Curve and Energy Density**

For a linear magnetic circuit,  $B = \mu H$  or  $H = B/\mu$ , energy density:

$$w_f = \int_0^B H dB = \int_0^B \frac{B}{\mu} dB = \frac{B^2}{2\mu}$$

and coenergy density:

$$w_{f}' = \int_{0}^{H} BdH = \int_{0}^{H} \mu HdH = \frac{\mu H^{2}}{2}$$

In this case, it is obvious that  $w_f = w_f$ .

\* Sen pg97

7/18/2018

Dr Awang Jusoh/Dr Makbul

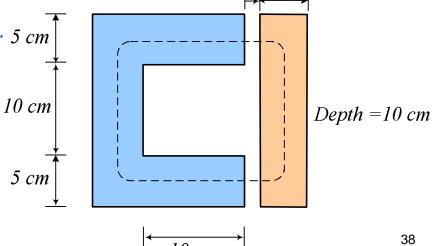

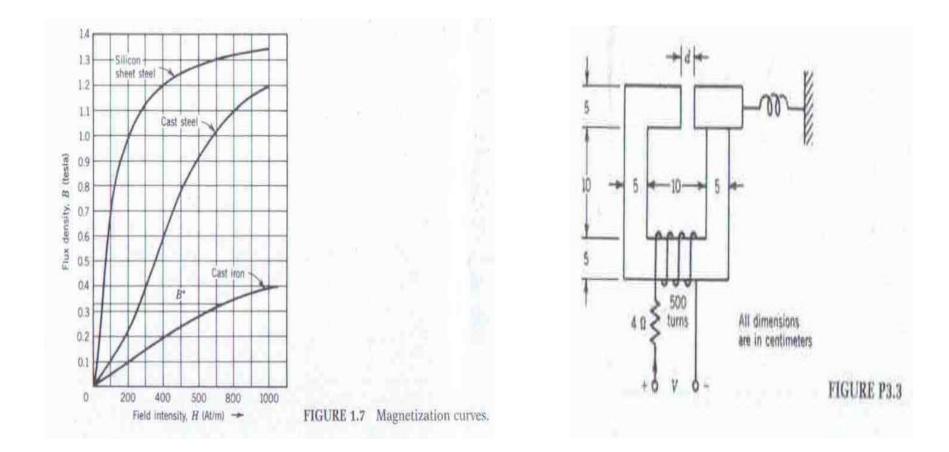

## Example 3.1 PC Sen

The dimensions of the relay system are shown in figure below. The magnetic core is made of cast steel whose B-H characteristic is shown in Figure 1.7 (pg.6). The coil has 300 turns, and the coil resistance is 6 ohms. For a fixed air-gap length  $I_g = 4 \text{ mm}$ , a dc source is connected to the coil to produce a flux density of 1.1 Tesla in the air-gap. Calculate

(a) The voltage of the dc source.  $_{5 cm}^{-7}$ (b) The stored field energy.

Pg:99 PC Sen

7/18/2018

## Example 3.2 PC Sen

The  $\lambda$ -*i* relationship for an electromagnetic system is given by

$$i = \left(\frac{\lambda g}{0.09}\right)^2$$

which is valid for the limits 0 < *i* < 4 A and 3 < g < 10 cm. For current *i* = 3A and air gap length *g* = 5 cm, find the mechanical force on the moving part using coenergy and energy of the field.

-124.7 Nm pg103 sen

# Example 3.3 PC Sen

The magnetic system shown in the Figure has the following parameters: N = 400, i = 3 AWidth of air-gap = 2.5 cm Length of air-gap = 1.5 mm

Neglect the reluctance of the core, leakage flux and the fringing flux. Determine:

- (a) The force of attraction between both sides of the air-gap

- (b) The energy stored in the air-gap.

- (c) Coil Inductance

Sen pg 106

A<sub>g</sub>

## Example 3.4 PC Sen

The lifting magnetic system is shown, with a square cross section area 6 x 6 cm<sup>2</sup>. The coil has 300 turns and a resistance of 6 ohms. Neglect core reluctance and fringing effect. a) The air gap is initially 5mm and a dc source of 120 V is connected to the coil. Determine the stored field energy and the lifting force b) The air gap is held at 5 mm and an ac source of 120 Vrms at 60 Hz is supplied to the coil. Determine the average value of the lift force Sen 107

- Q. The magnetic circuit shown in Figure Q1 is made of high permeability steel so that its reluctance can be negligible. The movable part is free to move about an x-axis. The coil has 1000 turns, the area normal to the flux is (5 cm  $\times$  10 cm), and the length of a single air gap is 5 mm.

- (i) Derive an expression for the inductance, L, as a function of air gap, g.

- (ii) Determine the force, Fm, for the current i = 10 A.

(iii) The maximum flux density in the air gaps is to be limited to approximately 1.0 Tesla to avoid excessive saturation of the steel. Compute the maximum force.

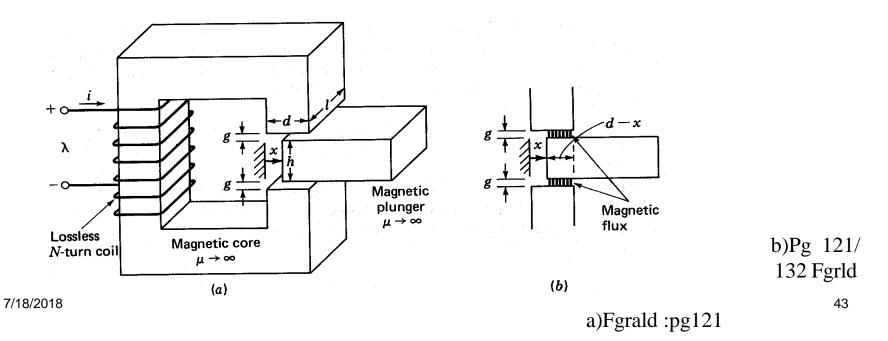

Figure below shows a relay made of infinitely-permeable magnetic material with a moveable plunger (infinitely-permeable material). The height of the plunger is much greater than air gap length (h>>g). Calculate

a) The magnetic storage energy  $W_f$  as a function of plunger position ( 0 < x < d) for N = 1000 turns, g = 2 mm, d= 0.15 m,  $\iota$ = 0.1 m and i = 10 A.

b) The generated force,  $F_m$

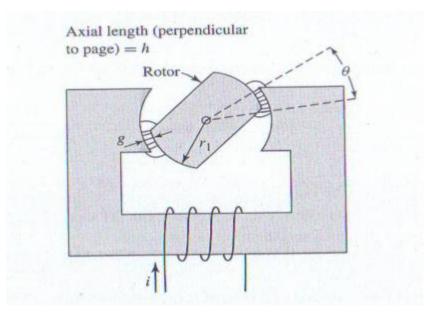

The magnetic circuit shown is made of high-permeability electrical steel. Assume the reluctance of steel  $\mu$  -- infinity. Derive the expression for the torque acting on the rotor .

Fgrd pg 135

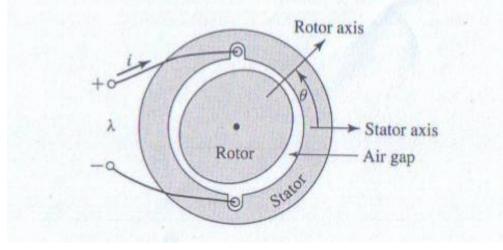

The magnetic circuit below consists of a single coil stator and an oval rotor. Because of the air-gap is non uniform, the coil inductance varies with the rotor angular position. Given coil inductance  $L(\theta) = Lo + L2cos2\theta$ , where Lo= 10.6mH and L2= 2.7 mH.

Find torque as a function of  $\theta$  for a coil current of 2 A.

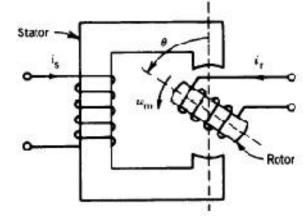

#### Exercise- PC Sen pg 115, prob.3.3

- An actuator system is shown. All dimensions are in cm. The magnetic material is cast steel, magnetisation as shown. The magnetic core and air gap have a square cross-section area. The coil has 500 turns and 4 ohm resistance.

- a) The gap is d = 1mm

- i) Determine the coil current and supply voltage required to establish an air gap flux density of 0.5 T

- ii. Determine the stored energy in the actuator system

- iii. Determine the force of attraction on the armature arm

- iv. Determine the coil inductance

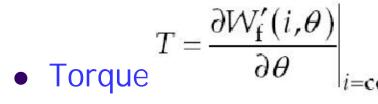

Doubly-excited Systems

# Energy, Coenergy and Force or Torque

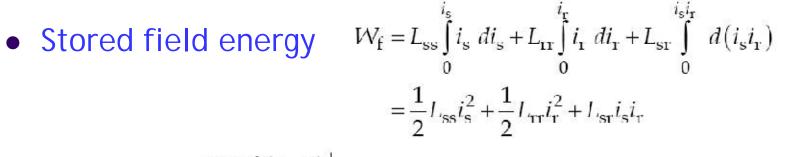

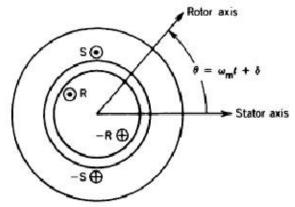

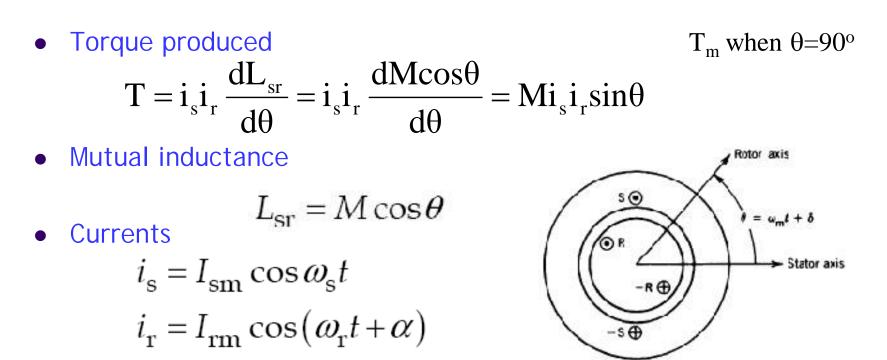

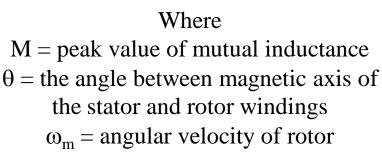

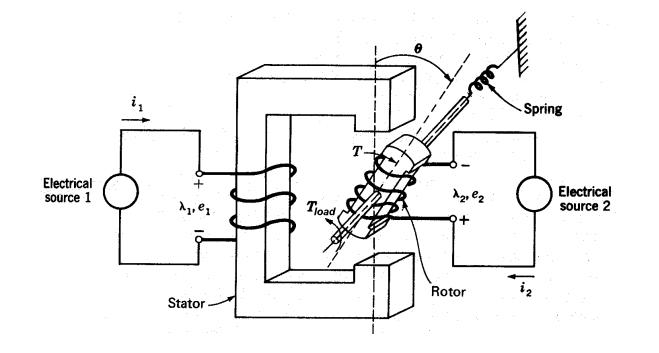

# **Rotating Machines**

- Most of the energy converters, particularly the higher-power ones, produce rotational motion.

- The essential part of a rotating electromagnetic system is shown in the figure.

- The fixed part is called the *stator*, the moving part is called the *rotor*.

- The rotor is mounted on a shaft and is free to rotate between the poles of the stator

- Let consider general case where both stator & rotor have windings carrying current ( i<sub>s</sub> and i<sub>r</sub> )

# **Rotating Machines**

- Assume general case, both stator and rotor have winding carrying currents (non-uniform air gap silent pole rotor)

- The system stored field energy, W<sub>f</sub> can be evaluated by establishing the stator current i<sub>s</sub> and rotor current i<sub>r</sub> and let system static, i.e. no mechanical output

$$dW_{f} = e_{s}i_{s} dt + e_{r}i_{r} dt$$

$$= i_{s} d\lambda_{s} + i_{r} d\lambda_{r}$$

$$\lambda_{s} = L_{ss}i_{s} + L_{sr}i_{r}$$

$$\lambda_{r} = L_{rs}i_{s} + L_{rr}i_{r}$$

$$\begin{vmatrix}\lambda_{s}\\\lambda_{r}\end{vmatrix} = \begin{vmatrix}I_{rs}i_{s} + L_{rr}i_{r}\\L_{sr} & L_{rr}\end{vmatrix} i_{r}$$

$$dW_{f} = i_{s} d(L_{cs}i_{s} + L_{cr}i_{r}) + i_{r} d(L_{sr}i_{s} + L_{r})$$

$$dW_{f} = i_{s} d(L_{cs}i_{s} + L_{cr}i_{r}) + i_{r} d(L_{sr}i_{s} + L_{r})$$

$$d\mathcal{W}_{f} = i_{s} d(L_{ss}i_{s} + L_{sr}i_{r}) + i_{r} d(L_{sr}i_{s} + L_{r}i_{r})$$

$$= L_{ss}i_{s} di_{s} + L_{rr}i_{r} di_{r} + L_{sr} d(i_{s}i_{r})$$

7/18/2018

In linear system, coenergy = energy  $W'_{f} = W_{f}$

$$T = \frac{1}{2}i_{\rm s}^2 \frac{dL_{\rm ss}}{d\theta} + \frac{1}{2}i_{\rm r}^2 \frac{dL_{\rm rr}}{d\theta} + i_{\rm s}i_{\rm r} \frac{dL_{\rm sr}}{d\theta}$$

• First two terms represents reluctance torque; variation of self inductance (exist in both salient stator and rotor, or in either stator or rotor is salient)

$X \rightarrow \theta$

• The third term represents alignment torque; variation of mutual inductance.

Reluctance Torque – It is caused by the tendency of the induced pole to align with excited pole such that the minimum reluctance is produced. At least one or both of the winding must be excited.

Alignment Torque – It is caused by a tendency of the excited rotor to align with excited stator so as to maximize the mutual inductance. Both winding must be excited.

- Reluctance machines are simple in construction, but torque developed in these machines is small.

- Cylindrical machines, although more complex in construction, produce larger torques.

- Most electrical machines are of the cylindrical type.

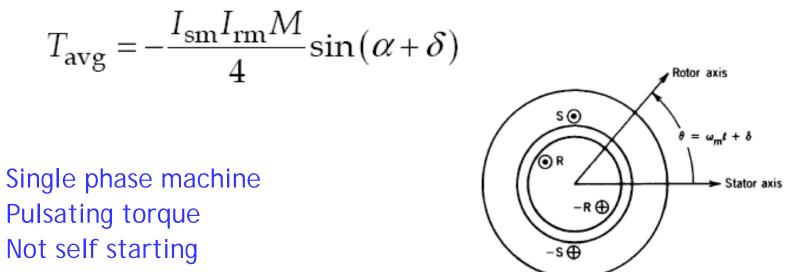

- A cross sectional view of an elementary two pole cylindrical rotating machine is (uniform air gap) shown.

- The stator and rotor windings are placed on two slots.

- In the actual machine the windings are distributed over several slots.

- If the effects of the slots are neglected, the reluctance of the magnetic path is independent of the position of the rotor.

- Assumed L<sub>ss</sub> and L<sub>rr</sub> are constant (i.e no reluctance torque produced).

- Alignment torque is caused by the tendency of the excited rotor to align with the excited stator, depends on <sup>7/18/2018</sup> mutual inductance

Rotor position

$$\theta = \omega_{\rm m} t + \delta$$

7/18/2018

$T = -I_{sm}I_{rm}M\cos\omega_{s}t\cos(\omega_{r}t + \alpha)\sin(\omega_{m}t + \delta)$

$$T = -\frac{I_{\rm sm}I_{\rm rm}M}{4} \begin{bmatrix} \sin\left\{\left(\omega_{\rm m} + \left(\omega_{\rm s} + \omega_{\rm r}\right)\right)t + \alpha + \delta\right\} + \\ \sin\left\{\left(\omega_{\rm m} - \left(\omega_{\rm s} + \omega_{\rm r}\right)\right)t - \alpha + \delta\right\} + \\ \sin\left\{\left(\omega_{\rm m} + \left(\omega_{\rm s} - \omega_{\rm r}\right)\right)t - \alpha + \delta\right\} + \\ \sin\left\{\left(\omega_{\rm m} - \left(\omega_{\rm s} - \omega_{\rm r}\right)\right)t + \alpha + \delta\right\} \end{bmatrix} \end{bmatrix}$$

- Torque in general varies sinusoidally with time

- Average value of each term is zero unless the coefficient of t is zero

• Non zero average torque exists/develop only if

$$\omega_{\rm m} = \pm (\omega_{\rm s} \pm \omega_{\rm r}) |\omega_{\rm m}| = |\omega_{\rm s} \pm \omega_{\rm r}|$$

Machine develop torque if sum or difference of the angular speed of the stator and rotor current

Case 1:

$$\omega_r = 0$$

$\omega_m = \omega_s$   $\alpha = 0$

Synchronous machine  $Wr = 0 - \omega_s$

Wr = 0 - Idc at rotor $T = -\frac{I_{\rm sm}I_{\rm R}M}{2} \{\sin(2\omega_{\rm s}t + \delta) + \sin\delta\}$

$$T_{\rm avg} = -\frac{I_{\rm sm}I_{\rm R}M}{2}\sin\delta$$

- Single phase machine

- Pulsating torque

• Polyphase machine minimize pulsating τorque

• Not self starting ( $\omega_m = 0 \rightarrow T_{avg} = 0$

• Asynchronous machines  $\omega_m = \omega_s - \omega_r$   $\omega_m \neq \omega_r$   $\omega_m \neq \omega_s$

$$T = -\frac{I_{\rm sm}I_{\rm rm}M}{4} \begin{bmatrix} \sin(2\omega_{\rm s}t + \alpha + \delta) + \sin(-2\omega_{\rm r}t - \alpha + \delta) + \\ \sin(2\omega_{\rm s}t - 2\omega_{\rm r}t - \alpha + \delta) + \sin(\alpha + \delta) \end{bmatrix}$$

• Polyphase machine minimize pulsating torque and self starting

- In a electromagnetic system, the rotor has no winding (i.e. we have a reluctance motor) and the inductance of the stator as a function of the rotor position  $\theta$  is  $L_{ss} = L_0 + L_2 \cos 2\theta$ . The stator current is  $i_s = I_{sm} \sin \omega t$

- (a) Obtain an expression for the torque acting on the rotor

- (b) Let  $\theta = \omega_m t + \delta$ , where  $\omega_m$  is the angular velocity of the rotor and  $\delta$  is the rotor position at t = 0. Find the condition for the non-zero average torque and obtain the expression for the average torque.

In a doubly excited rotating actuator shown in figure below, the stator inductances are given as  $L_{11} = (3+\cos 2\theta)$ mH,  $L_{12} = 0.3\cos\theta$ , and the rotor impedance is  $L_{22} =$  $30+10\cos 2\theta$ . Find the developed torque in the system for  $i_1=0.8A$  and  $i_2 = 0.01 A$ .

Fgrd pg 140

7/18/2018

60

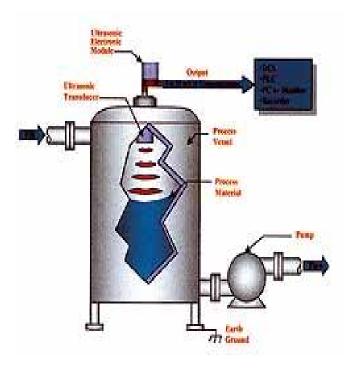

# LEVEL MEASUREMENT

By N Harathi

Assistant Professor Electronics and Instrumentation Engineering

Unit: II Course: Industrial Instrumentation – II Target Group: III B.Tech. EIE

## LEVEL MEASUREMENT

- With the wide variety of approaches to level measurement and as many as 163 suppliers offering one or more types of level-measuring instrument, identifying the right one for your application can be very difficult. In recent years, technologies that capitalized on microprocessor developments have stood out from the pack.

- For example, the tried-and-true technique of measuring the head of a liquid has gained new life thanks to "smart" differential pressure (DP) transmitters. Today's local level-measuring instruments can include diagnostics as well as configuration and process data that can be communicated over a network to remote monitoring and control instrumentation. One model even provides local PID control.

**III EIE- Industrial Instrumentation**

# LEVEL MEASUREMENT

- Some of the most commonly used liquid-level measurement methods are:

- FLOAT type

- RF capacitance

- Conductance (conductivity)

- Hydrostatic head/tank gauging

- Radar

- Ultrasonic

- Before you can decide which one is right for your application, however, you need to understand how each works and the theory behind it.

#### Float type Level transmitter

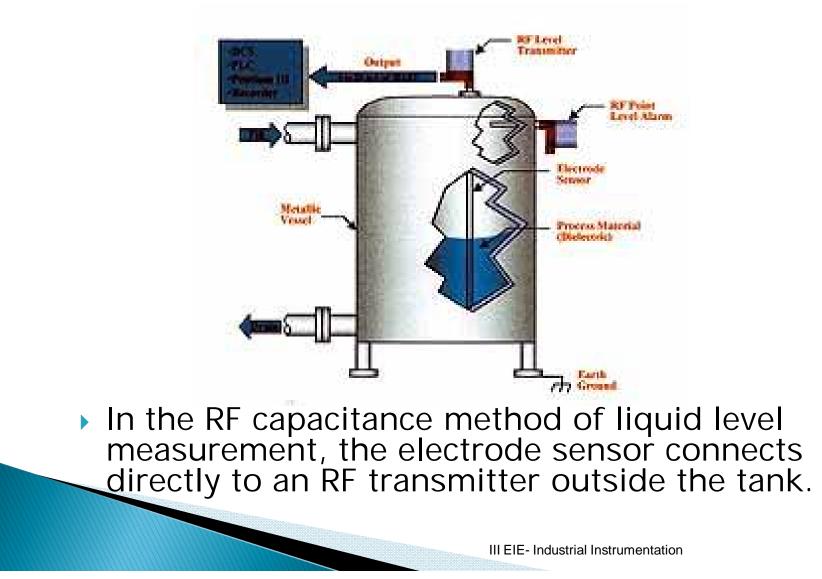

## **RF** Capacitance

- RF (radio frequency) technology uses the electrical characteristics of a capacitor, in several different configurations, for level measurement.

- Commonly referred to as RF capacitance or simply RF, the method is suited for detecting the level of liquids, slurries, granulars, or interfaces contained in a vessel.

- Designs are available for measuring process level at a specific point, at multiple points, or continuously over the entire vessel height. Radio frequencies for all types range from 30 kHz to 1 MHz.

**III EIE- Industrial Instrumentation**

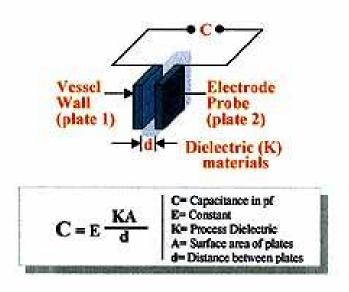

- All RF level systems make use of enhancements of the same capacitance-measuring technique, and the same basic theory underlies them all.

- An electrical capacitance exists between two conductors separated by a distance, d. The first conductor can be the vessel wall (plate 1), and the second can be a measurement probe or electrode (plate 2). The two conductors have an effective area, A, normal to each other.

- Between the conductors is an insulating medium—the nonconducting material involved in the level measurement.

**III EIE- Industrial Instrumentation**

- The amount of capacitance here is determined not only by the spacing and area of the conductors, but also by the electrical characteristic (relative dielectric constant, K) of the insulating material.

- The value of K affects the charge storage capacity of the system: The higher the K, the more charge it can build up.

- Dry air has a K of 1.0. Liquids and solids have considerably higher values, as shown in Table 1.

The capacitance for the basic capacitor arrangement shown in Figure 1 can be computed from the equation:

$$C = E (K A/d)$$

where:

- C = capacitance in picofarads (pF)

- E = a constant known as the absolute permittivity of free space

- K = relative dielectric constant of the insulating material

- A = effective area of the conductors

- d = distance between the conductors

**III EIE- Industrial Instrumentation**

- To apply this formula to a level-measuring system, you must assume that the process material is insulating, which, of course, is not always true.

- A bare, conductive, sensing electrode (probe) is inserted down into a tank to act as one conductor of the capacitor.

- The metal wall of the tank acts as the other.

- If the tank is nonmetallic, a conductive ground reference must be inserted into the tank to act as the other capacitor conductor.

- With the tank empty, the insulating medium between the two conductors is air. With the tank full, the insulating material is the process liquid or solid.

- As the level rises in the tank to start covering the probe, some of the insulating effect from air changes into that from the process material, producing a change in capacitance between the sensing probe and ground.

- This capacitance is measured to provide a direct, linear measurement of tank level.

**III EIE- Industrial Instrumentation**

- The electrode sensor, or probe, connects directly to an RF level transmitter, which is mounted outside the tank. In one design, with the probe mounted vertically, the system can be used for both continuous level measurement and simultaneous multipoint level control.

- Alternatively, for point level measurement, one or more probes can be installed horizontally through the side of the tank; Figure shows this type being used as a high-level alarm.

#### TABLE 1

#### **Dielectric Constants of Sample Substances**

| Substance         | Value |

|-------------------|-------|

|                   | 18.3  |

| Isopropyl alcohol | 1.8   |

| Kerosene          | 8.0   |

| Kynar             | 2.1   |

| Mineral oil       | 80    |

| Pure water        | 4.0   |

| Sand              | 3.0   |

| Sugar             | 2.0   |

| Teflon            | 2.0   |

This view of a typical RF capacitance probe shows the electronic chassis enlarged to twice the size of its housing.

#### **RF Impedance or RF Admittance.**

- When another electrical characteristic, impedance, enters the picture, the result is further refinements in RF level measurement.

- Offering improved reliability and a wider range of uses, these variations of the basic RF system are called RF admittance or RF impedance. In RF or AC circuits, impe dance, Z, is defined as the total opposition to current flow:

$$Z = R + 1/j 2 \pi f C$$

where:

- R = resistance in ohms

- f = measurement frequency (radio frequency for RF measurement)

- C = capacitance in picofarads

#### **RF Impedance or RF Admittance.**

- An RF impedance level-sensing instrument measures this total impedance rather than just the capacitance. Some level-measuring systems are referred to as RF admittance types. Admittance, A, is defined as a measure of how readily RF or AC current will flow in a circuit and is therefore the reciprocal of impedance (A = 1/Z). Thus, there is no basic difference between the RF impedance and RF admittance as a level-measurement technology.

In some cases, the process material tends to build

- In some cases, the process material tends to build up a coating on the level-sensing probe. In such cases, which are not uncommon in level applications, a significant measurement error can occur because the instrument measures extra capacitance and resistance from the coating buildup. As a result, the sensor reports a higher, and incorrect, level instead of the actual tank level.

#### **RF Impedance or RF Admittance.**

- Note that the equation for impedance includes resistance, R. The RF impedance method can be provided with specific circuitry capable of measuring the resistance and capacitance components from the coating and the capacitive component due to the actual process material level.

- The circuitry is designed to solve a mathematical relationship electronically, thereby producing a 4– 20 mA current output that is proportional only to the actual level of the process material. It is virtually unaffected by any buildup of coating on the sensing probe, enabling an RF system to continue functioning reliably and accurately.

#### Conductance

- The conductance method of liquid level measurement is based on the electrical conductance of the measured material, which is usually a liquid that can conduct a current with a low-voltage source (normally <20 V). Hence the method is also referred to as a conductivity system. Conductance is a relatively low-cost, simple method to detect and control level in a vessel.

- One common way to set up an electrical circuit is to use a dual-tip probe that eliminates the need for grounding a metal tank. Such probes are generally used for point level detection, and the detected point can be the interface between a conductive and nonconductive liquid.

#### Conductance

- The conductance method of liquid level measurement is based on the electrical conductance of the measured material, which is usually a liquid that can conduct a current with a low-voltage source (normally <20 V). Hence the method is also referred to as a conductivity system. Conductance is a relatively low-cost, simple method to detect and control level in a vessel.

- One common way to set up an electrical circuit is to use a dual-tip probe that eliminates the need for grounding a metal tank. Such probes are generally used for point level detection, and the detected point can be the interface between a conductive and nonconductive liquid.

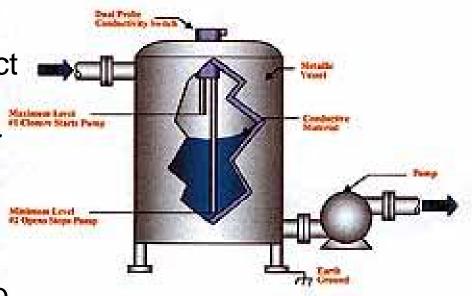

- Figure 3 shows an arrangement with two dual-tip probes that detect maximum and minimum levels. When the level reaches the upper probe, a switch closes to start the discharge pump; when the level reaches the lower probe, the switch opens to stop the pump.

#### Conductance

Figure shows an arrangement with two dual-tip probes that detect maximum and minimum levels. When the level reaches the upper probe, a switch closes to start the discharge pump; when the level reaches the lower probe, the switch opens to stop the pump

In the conductive type of level measurement, two dual-tip probes detect the maximum and minimum levels in a tank.

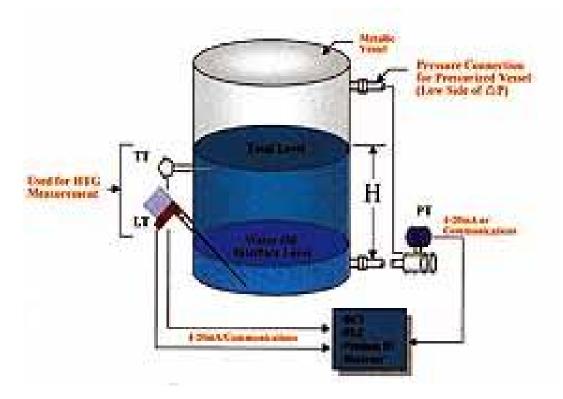

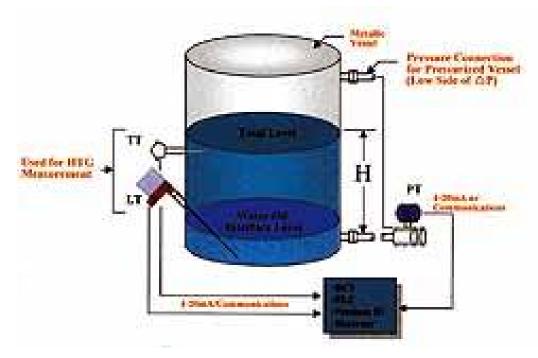

### Hydrostatic Head

- One of the oldest and most common methods of measuring liquid level is to measure the pressure exerted by a column (or head) of liquid in the vessel. The basic relationships are:

- H = mP/d

- where, in consistent units:

- P = pressure

- m = a constant

- H = head

- d = density

## Hydrostatic Head

- The density of a liquid varies with temperature. For the highest precision in level measurement, the density must therefore be compensated for or expressed with relation to the actual temperature of the measured liquid.

- For decades, DP-type instruments—long before the DP cell—were used to measure liquid.

- With open vessels a pipe at or near the bottom of the vessel connects only to the high-pressure side of the meter body and the low-pressure side is open to the atmosphere.

- If the vessel is pressurized or under vacuum, the low side of the meter has a pipe connection near the top of the vessel, so that the instrument responds only to changes in the head of liquid.

Figure shows a simplified system that incorporates only one pressure transmitter (PT) with a temperature transmitter (TT) and makes novel use of a level transmitter (LT) to detect accumulation of water at the bottom of a tank.

Mass (weight) of the tank's contents can be calculated from the hydrostatic head (measured by PT) multiplied by the tank area (obtained from a lookup table). The liquid's temperature-density relationship can be used to calculate the volume and level, provided the tank is not under pressure. Data fed into a computer system make it possible for all calculations to be automatic, with results continuously available for monitoring and accounting purposes.

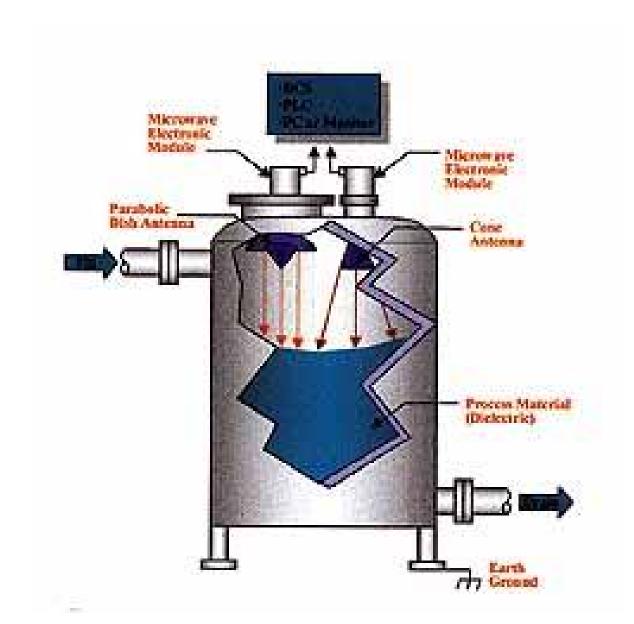

- Radar methods of level measurement are sometimes referred to as microwave types. Both use electromagnetic waves, typically in the microwave X-band (10 GHz) range. This technology is being adapted and refined for level measurement, so you should check out the latest offerings. Most applications have been designed for continuous level measurement.

- Basically, all types operate on the principle of beaming microwaves downward from a sensor located on top of the vessel. The sensor receives back a portion of the energy that is reflected off the surface of the measured medium. Travel time for the signal (called the time of flight) is used to determine level. For continuous level measurement, there are two main types of noninvasive systems, as well as one invasive type that uses a cable or rod as a wave guide and extends down into the tank's contents to near its bottom

- One type of noninvasive system uses a technology called frequency-modulated continuous wave (FMCW).

- From an electronic module on top of the tank, a sensor oscillator sends down a linear frequency sweep, at a fixed bandwidth and sweep time.

- The reflected radar signal is delayed in proportion to the distance to the level surface.

- Its frequency is different from that of the transmitted signal, and the two signals blend into a new frequency proportional to distance. That new frequency is converted into a very accurate measure of liquid level.

- The sensor outputs a frequency-modulated (FM) signal that varies from 0 to ~200 Hz as the distance ranges from 0 to 200 ft (60 m).

- An advantage of this technique is that the level-measurement signals are FM rather than AM, affording the same advantages that radio waves offer.

- Most tank noise is in the AM range and does not affect the FM signals.

- The second noninvasive technology, pulsed radar or pulsed time-of-flight, operates on a principle very similar to that of the ultrasonic pulse method. The radar pulse is aimed at the liquid's surface and the transit time of the pulse's re turn is used to calculate level. Because pulse radar is lower power than FMCW, its performance can be affected by obstructions in the tank as well as foam and lowdielectric materials (K < 2).</p>

- Antennas for the noninvasive methods come in two designs: parabolic dish and cone.

- The parabolic dish antenna tends to direct the signals over a wider area while the cone tends to confine the signals in a narrower downward path. The choice of one or the other, and its diameter, depends on application factors such as tank obstructions that may serve as reflectors, the presence of from, and turbulence. Of the measured fluid

Radar (microwave) level measurement can use either

ever.

Guided-wave radar (GWR) is an invasive method that uses a rod or cable to guide the micro wave as it passes down from the sensor into the material being measured and all the way to the bottom of the vessel. The basis for GWR is time-domain reflectometry (TDR), which has been used for years to locate breaks in long lengths of cable that are underground or in building walls. A TDR generator develops more than 200,000 pulses of electromagnetic energy that travel down the waveguide and back. The dielectric of the measured fluid causes a change in impedance that in turn develops a wave reflection. Transit time of pulses down and back is used as a measure of

#### Ultrasonic and Sonic

- Both ultrasonic and sonic level instruments operate on the basic principle of using sound waves to determine fluid level. The frequency range for ultrasonic methods is ~20–200 kHz, and sonic types use a frequency of 10 kHz.

- A top-of-tank mounted transducer directs waves downward in bursts onto the surface of the material whose level is to be measured. Echoes of these waves return to the transducer, which performs calculations to convert the distance of wave travel into a measure of level in the tank.

- A piezoelectric crystal inside the transducer converts electrical pulses into sound energy that travels in the form of a wave at the established frequency and at a constant speed in a given medium. The medium is normally air over the material's surface but it could be a blanket of nitrogen or some other vapor.

- The sound waves are emitted in bursts and received back at the transducer as echoes. The instrument measures the time for the bursts to travel down to the reflecting surface and return. This time will be proportional to the distance from the transducer to the surface and can be used to determine the level of fluid in the tank. For practical applications of this method, you must consider a number of factors. A few key points are:

- The speed of sound through the medium (usually air) varies with the medium's temperature. The transducer may contain a temperature sensor to compensate for changes in operating temperature that would alter the speed of sound and hence the distance calculation that determines an accurate level measurement.

- The presence of heavy foam on the surface of the material can act as a sound absorbent. In some cases, the absorption may be sufficient to preclude use of the ultrasonic technique.

- Extreme turbulence of the liquid can cause fluctuating readings. Use of a damping adjustment in the instrument or a response delay may help overcome this problem.

# **Combinational Logic**

ΒY

Dr.G. Sunitha Topic: Combinational Logic Subject: Digital Logic and Design(DLD) II-B.Tech(CSE) Sree Vidyanikethan Engineering College

II BTech(CSE)

Combinational Logic

#### **Combinational Logic**

- Logic circuits for digital systems may be combinational or sequential.

- A combinational circuit consists of input variables, logic gates, and output variables.

Fig. 4-1 Block Diagram of Combinational Circuit

II BTech(CSE)

Combinational Logic

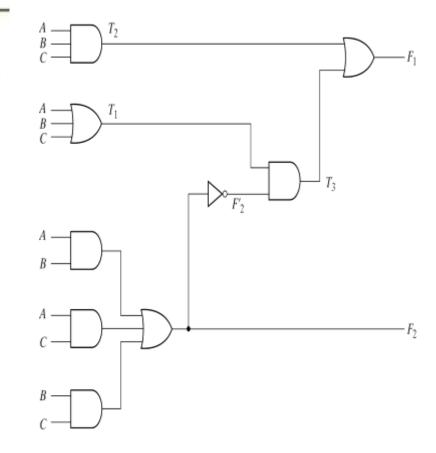

# Analysis procedure

- To obtain the output Boolean functions from a logic diagram, proceed as follows:

- 1. Label all gate outputs that are a function of input variables with arbitrary symbols. Determine the Boolean functions for each gate output.

- 2. Label the gates that are a function of input variables and previously labeled gates with other arbitrary symbols. Find the Boolean functions for these gates.

# Analysis procedure

- 3. Repeat the process outlined in step 2 until the outputs of the circuit are obtained.

- 4. By repeated substitution of previously defined functions, obtain the output Boolean functions in terms of input variables.

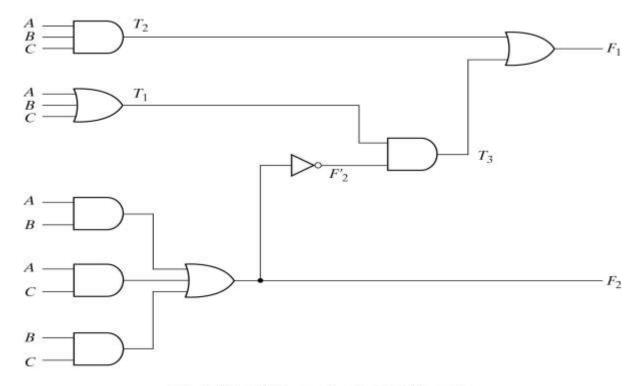

#### Example

$F_2 = AB + AC + BC; T_1 = A + B + C; T_2 = ABC; T_3 = F_2'T_1;$   $F_1 = T_3 + T_2$  $F_1 = T_3 + T_2 = F_2'T_1 + ABC = A'BC' + A'B'C + AB'C' + ABC$

Fig. 4-2 Logic Diagr Combinational Logic

# Derive truth table from logic diagram

We can derive the truth table in Table 3-1 by using the circuit of Fig.3-2.

Table 4-1 Truth Table for the Logic Diagram of Fig. 4-2

| A | В         | с    | F2 | <b>F</b> '2 | T <sub>1</sub> | T2 | T <sub>3</sub> | F <sub>1</sub> |

|---|-----------|------|----|-------------|----------------|----|----------------|----------------|

| 0 | 0         | 0    | 0  | 1           | 0              | 0  | 0              | 0              |

| 0 | 0         | 1    | 0  | 1           | 1              | 0  | 1              | 1              |

| 0 | 1         | 0    | 0  | 1           | 1              | 0  | 1              | 1              |

| 0 | 1         | 1    | 1  | 0           | 1              | 0  | 0              | 0              |

| 1 | 0         | 0    | 0  | 1           | 1              | 0  | 1              | 1              |

| 1 | 0         | 1    | 1  | 0           | 1              | 0  | 0              | 0              |

| 1 | 1         | 0    | 1  | 0           | 1              | 0  | 0              | 0              |

| 1 | 1         | 1    | 1  | 0           | 1              | 1  | 0              | 1              |

|   | II BTech( | CSE) |    | Combinatio  | nal Logic      |    |                |                |

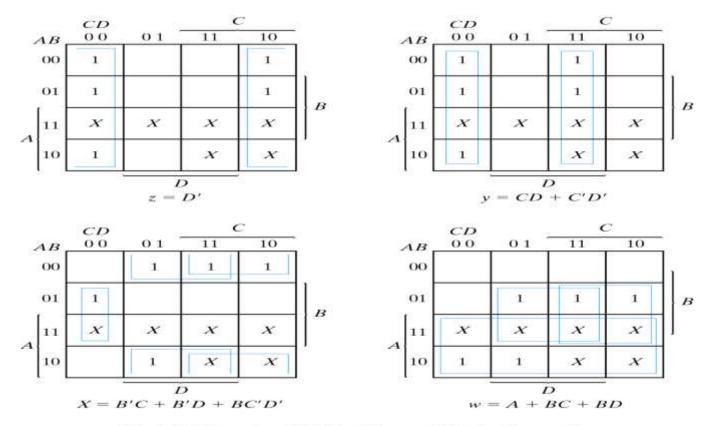

## Design procedure

1. Table3-2 is a Code-Conversion example, first, we can list the relation of the BCD and Excess-3 codes in the truth table.

|         | Input | BCD |    | Output Excess-3 Code |       |   |   |  |

|---------|-------|-----|----|----------------------|-------|---|---|--|

| A       | B     | с   | D  | w                    | x     | y | z |  |

| 0       | 0     | 0   | 0  | 0                    | 0     | 1 | 1 |  |

| 0       | 0     | 0   | 1  | 0                    | 1     | 0 | 0 |  |

| 0       | 0     | 1   | 0  | 0                    | 1     | 0 | 1 |  |

| 0       | 0     | 1   | 1  | 0                    | 1     | 1 | 0 |  |

| 0       | 1     | 0   | 0  | 0                    | 1     | 1 | 1 |  |

| 0       | 1     | 0   | 1  | 1                    | 0     | 0 | 0 |  |

| 0       | 1     | 1   | 0  | 1                    | 0     | 0 | 1 |  |

| 0       | 1     | 1   | 1  | 1                    | 0     | 1 | 0 |  |

| 1       | 0     | 0   | 0  | 1                    | 0     | 1 | 1 |  |

| 1       | 0     | 0   | 1  | 1                    | 1     | 0 | 0 |  |

| [ BTech | (CSE) |     | C( | ombinational         | Logic |   | _ |  |

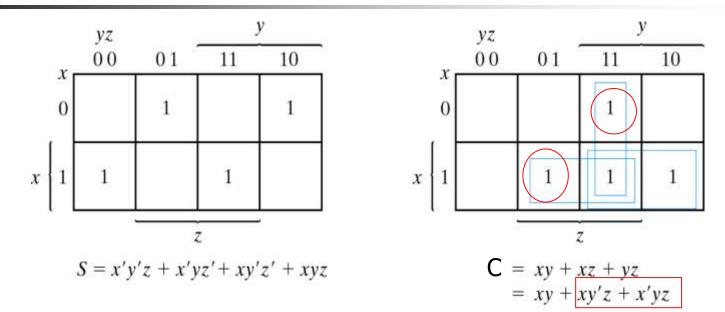

## Karnaugh map

2. For each symbol of the Excess-3 code, we use 1's to draw the map for simplifying Boolean function.

II BTech (CSE) Fig. 4-3 Maps for BCD Combinational Cogic Converter

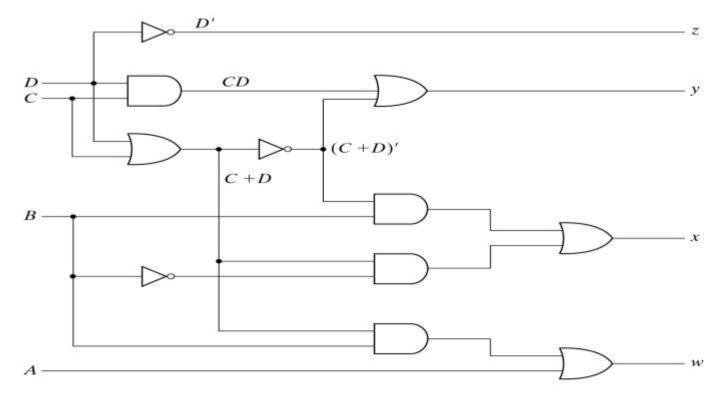

#### **Circuit implementation**

z = D'; y = CD + C'D' = CD + (C + D)'x = B'C + B'D + BC'D' = B'(C + D) + B(C + D)'w = A + BC + BD = A + B(C + D)

II BTech(CSE) Fig. 4-4 Logic Diagram Combinational Logic Code Converter

#### **Binary Adder-Subtractor**

- A combinational circuit that performs the addition of two bits is called a half adder.

- The truth table for the half adder is listed below:

Table 4-3

Combinational Logic

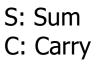

#### **Implementation of Half-Adder**

Fig. 4-5 Implementation of Half-Adder

II BTech(CSE)

**Combinational Logic**

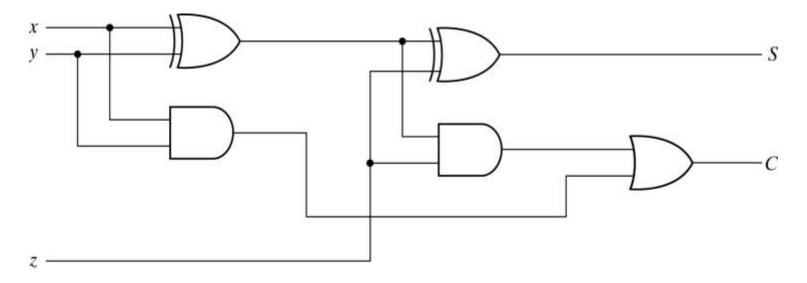

**Full-Adder**

One that performs the addition of three bits(two significant bits and a previous carry) is a full adder.

#### Table 4-4 Full Adder

| x                      | Y | z | с          | 5 |  |  |  |

|------------------------|---|---|------------|---|--|--|--|

| 0                      | 0 | 0 | 0          | 0 |  |  |  |

| 0                      | 0 | 1 | 0          | 1 |  |  |  |

| 0                      | 1 | 0 | 0          | 1 |  |  |  |

| 0                      | 1 | 1 | 1          | 0 |  |  |  |

| 1                      | 0 | 0 | 0          | 1 |  |  |  |

| 1                      | 0 | 1 | 1          | 0 |  |  |  |

| 1                      | 1 | 0 | 1          | 0 |  |  |  |

| 1                      | 1 | 1 | 1          | 1 |  |  |  |

| BTech(CSE) Combination |   |   | onal Logic |   |  |  |  |

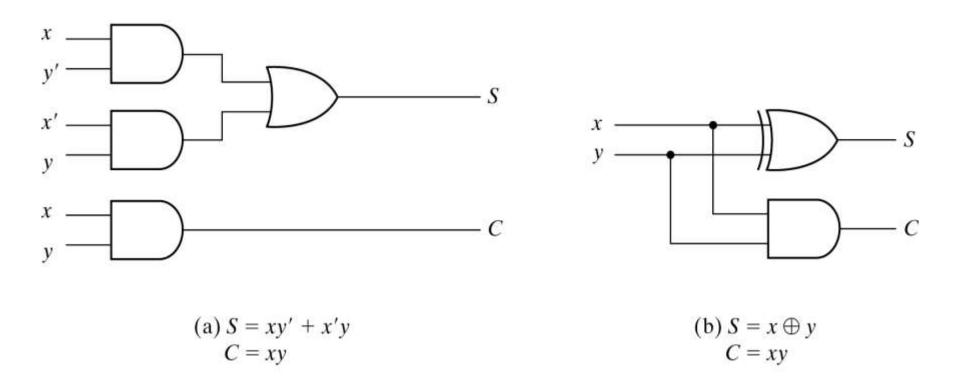

### Simplified Expressions

Fig. 4-6 Maps for Full Adder

$$S = x'y'z + x'yz' + xy'z' + xyz$$

$$C = xy + xz + yz$$

II BTech(CSE)

**Combinational Logic**

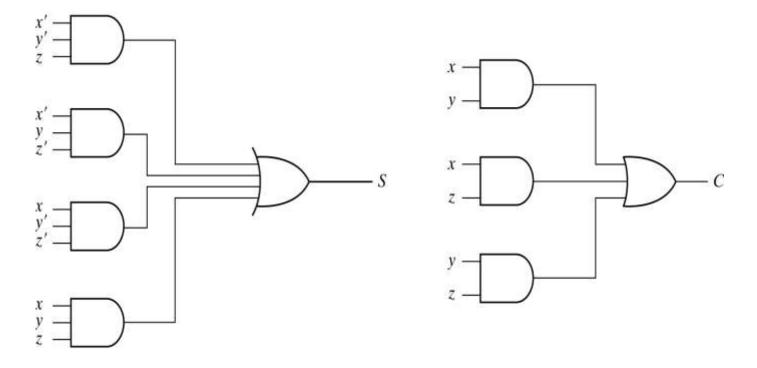

# Full adder implemented in SOP

Fig. 4-7 Implementation of Full Adder in Sum of Products

II BTech(CSE)

Combinational Logic

### Another implementation

Full-adder can also implemented with two half adders and one OR gate (Carry Look-Ahead adder).

$$S = z \bigoplus (x \bigoplus y)$$

= z'(xy' + x'y) + z(xy' + x'y)'

= xy'z' + x'yz' + xyz + x'y'z

$$C = z(xy' + x'y) + xy = xy'z + x'yz + xy$$

II BTECh (CSE)mplementation of Full Adder with Two Half Adders and an OR Gate

# Binary adder

This is also called **Ripple Carry** Adder , because of the construction with full adders are connected in cascade.

| Input carry 0 1 1 0 $C_i$<br>Augend 1 0 1 1 $A_i$<br>Addend 0 0 1 1 $B_i$<br>Sum 1 1 1 0 $S_i$<br>Output carry 0 0 1 1 $C_{i+1}$ | Subscript i: | 3 | 2   | 1                     | 0 |           |

|----------------------------------------------------------------------------------------------------------------------------------|--------------|---|-----|-----------------------|---|-----------|

| Addend0011 $B_i$ Sum1110 $S_i$ Output carry0011 $C_{i+1}$                                                                        | Input carry  | 0 | 1   | 1                     | 0 | $C_i$     |

| Sum $1$ $1$ $1$ $0$ $S_i$ Output carry $0$ $0$ $1$ $1$ $C_{i+1}$                                                                 | Augend       | 1 | 0   | 1                     | 1 | $A_i$     |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                            | Addend       | 0 | 0   | 1                     | 1 | $B_i$     |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                            | Sum          | 1 | 1   | 1                     | 0 | $S_i$     |

|                                                                                                                                  | Output carry | 0 | 0   | 1                     | 1 | $C_{i+1}$ |

|                                                                                                                                  |              | Г | ↓ ↓ | <i>C</i> <sub>1</sub> |   |           |

Fig. 4-9 4-Bit Adder Combinational Logic

II BTech(CSE)

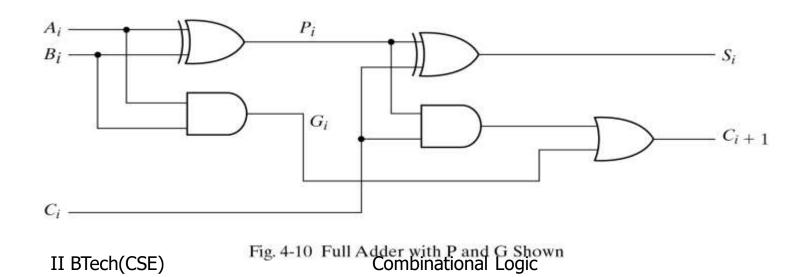

## **Carry Propagation**

- Fig.3-9 causes a unstable factor on carry bit, and produces a longest propagation delay.

- The signal from C<sub>i</sub> to the output carry C<sub>i+1</sub>, propagates through an AND and OR gates, so, for an n-bit RCA, there are 2n gate levels for the carry to propagate from input to output.

### **Carry Propagation**

- Because the propagation delay will affect the output signals on different time, so the signals are given enough time to get the precise and stable outputs.

- The most widely used technique employs the principle of carry look-ahead to improve the speed of the algorithm.

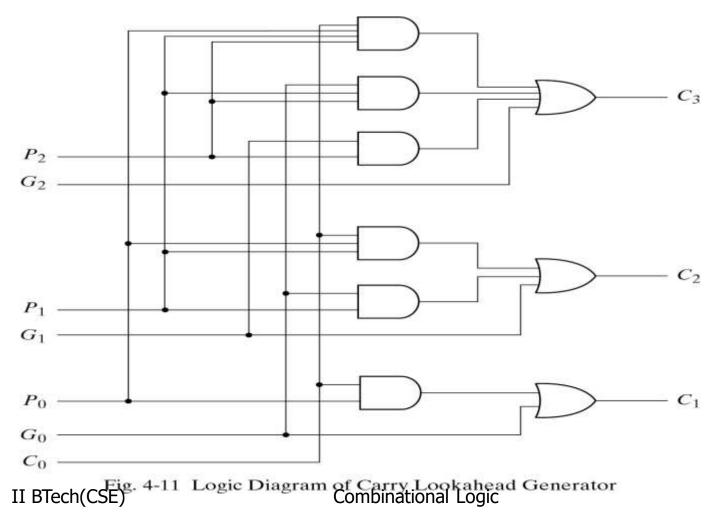

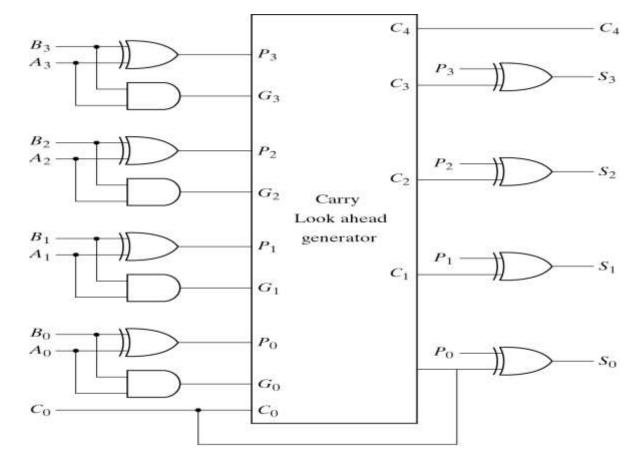

### **Boolean functions**

- $P_i = A_i \oplus B_i$  steady state value

- $G_i = A_i B_i$  steady state value

Output sum and carry

$$S_i = P_i \oplus C_i$$

$$C_{i+1} = G_i + P_iC_i$$

G<sub>i</sub> : carry generate P<sub>i</sub> : carry propagate

$$C_{0} = \text{input carry}$$

$$C_{1} = G_{0} + P_{0}C_{0}$$

$$C_{2} = G_{1} + P_{1}C_{1} = G_{1} + P_{1}G_{0} + P_{1}P_{0}C_{0}$$

$$C_{3} = G_{2} + P_{2}C_{2} = G_{2} + P_{2}G_{1} + P_{2}P_{1}G_{0} + P_{2}P_{1}P_{0}C_{0}$$

C<sub>3</sub> does not have to wait for C<sub>2</sub> and C<sub>1</sub> to propagate.

II BTech(CSE)

### Logic diagram of carry look-ahead generator

C<sub>3</sub> is propagated at the same time as C<sub>2</sub> and C<sub>1</sub>.

### 3-bit adder with carry lookahead

Delay time of n-bit CLAA = XOR + (AND + OR) + XOR

II BTech(CSE)

Fig. 4-12 4-Bit Adder with Carry Lookahead Combinational Logic

### **Binary subtractor**

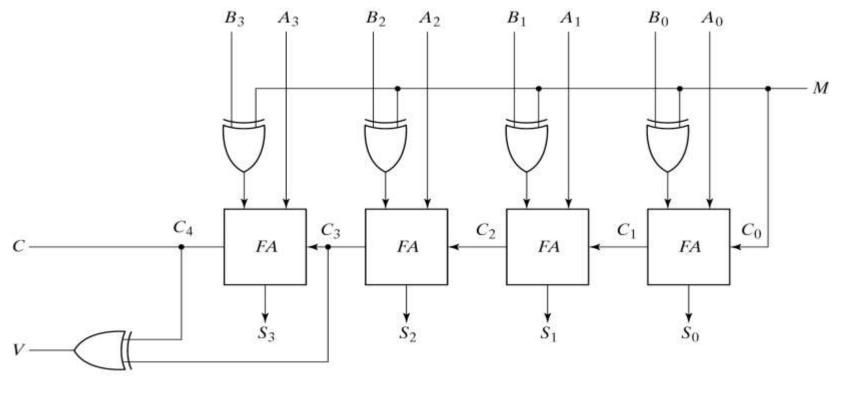

### $M = 1 \rightarrow subtractor$ ; $M = 0 \rightarrow adder$

Fig. 4-13 4-Bit Adder Subtractor

- It is worth noting Fig.3-13 that binary numbers in the signed-complement system are added and subtracted by the same basic addition and subtraction rules as unsigned numbers.

- Overflow is a problem in digital computers because the number of bits that hold the number is finite and a result that contains n+1 bits cannot be accommodated.

### Overflow on signed and unsigned

- When two unsigned numbers are added, an overflow is detected from the end carry out of the MSB position.

- When two signed numbers are added, the sign bit is treated as part of the number and the end carry does not indicate an overflow.

- An overflow cann't occur after an addition if one number is positive and the other is negative.

- An overflow may occur if the two numbers added are both positive or both negative.

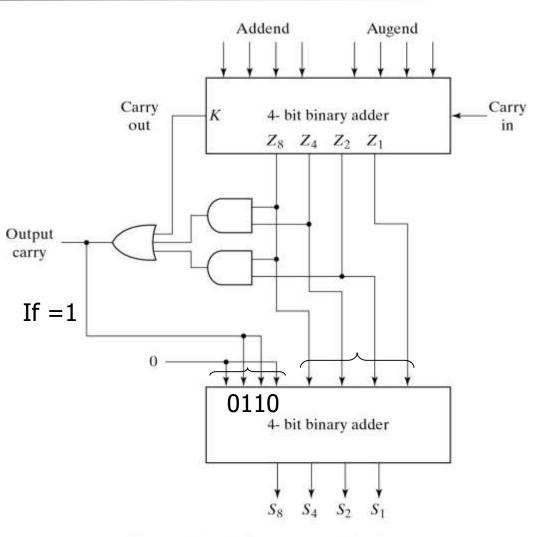

### Decimal adder

### BCD adder can't exceed 9 on each input digit. K is the carry.

#### Table 4-5 Derivation of BCD Adder

| Binary Sum |                |          |                |    |      | Decima         |            |    |                       |          |

|------------|----------------|----------|----------------|----|------|----------------|------------|----|-----------------------|----------|

| к          | Z <sub>8</sub> | ZA       | Z <sub>2</sub> | Z1 | С    | S <sub>8</sub> | <b>S</b> 4 | Sz | <i>S</i> <sub>1</sub> |          |

| 0          | 0              | 0        | 0              | 0  | 0    | 0              | 0          | 0  | 0                     | 0        |

| 0          | 0              | 0        | 0              | 1  | 0    | 0              | 0          | 0  | 1                     | 1        |

| 0          | 0              | 0        | 1              | 0  | 0    | 0              | 0          | 1  | 0                     | 2        |

| 0          | 0              | 0        | 1              | 1  | 0    | 0              | 0          | 1  | 1                     | 3        |

| 0          | 0              | 1        | 0              | 0  | 0    | 0              | 1          | 0  | 0                     | 4        |

| 0          | 0              | 1        | 0              | 1  | 0    | 0              | 1          | 0  | 1                     | 5        |

| 0          | 0              | 1        | 1              | 0  | 0    | 0              | 1          | 1  | 0                     | 6        |

| 0          | 0              | 1        | 1              | 1  | 0    | 0              | 1          | 1  | 1                     | 7        |

| 0          | 1              | 0        | 0              | 0  | 0    | 1              | 0          | 0  | 0                     | 8        |

| 0          | 1              | 0        | 0              | 1  | 0    | 1              | 0          | 0  | 1                     | 9        |

| 0          | 1              | 0        | 1              | 0  | 1    | 0              | 0          | 0  | 0                     | 10       |

| 0          | 1              | 0        | 1              | 1  | 1    | 0              | 0          | 0  | 1                     | 11       |

| 0          | 1              | 1        | 0              | 0  | 1    | 0              | 0          | 1  | 0                     | 12       |

| 0          | 1              | 1        | 0              | 1  | 1    | 0              | 0          | 1  | 1                     | 13       |

| 0          | 1              | 1        | 1              | 0  | 1    | 0              | 1          | 0  | 0                     | 14       |

| 0          | 1              | 1        | 1              | 1  | 1    | 0              | 1          | 0  | 1                     | 15       |

| 1          | 0              | 0        | 0              | 0  | 1    | 0              | 1          | 1  | 0                     | 16       |

| 1          | 0              | 0        | 0              | 1  | 1    | 0              | 1          | 1  | 1                     | 17       |

| 1          | 0              | 0        | 1              | 0  | 1    | 1              | 0          | 0  | 0                     | 18       |

| 1          | 0              | 0        | 1              | 1  | 1    | 1              | 0          | 0  | 1                     | 19       |

|            | II             | BTech(CS | SE)            |    | Comb | vinational     | Logic      |    |                       | <u> </u> |

### Rules of BCD adder

- When the binary sum is greater than 1001, we obtain a non-valid BCD representation.

- The addition of binary 6(0110) to the binary sum converts it to the correct BCD representation and also produces an output carry as required.

- To distinguish them from binary 1000 and 1001, which also have a 1 in position Z<sub>8</sub>, we specify further that either Z<sub>3</sub> or Z<sub>2</sub> must have a 1.

$$C = K + Z_8 Z_3 + Z_8 Z_2$$

### Implementation of BCD adder

- A decimal parallel adder that adds n decimal digits needs n BCD adder stages.

- The output carry from one stage must be connected

to the input carry of the next higherorder stage.

Combinational<sup>4</sup>LogRock Diagram of a BCD Adder

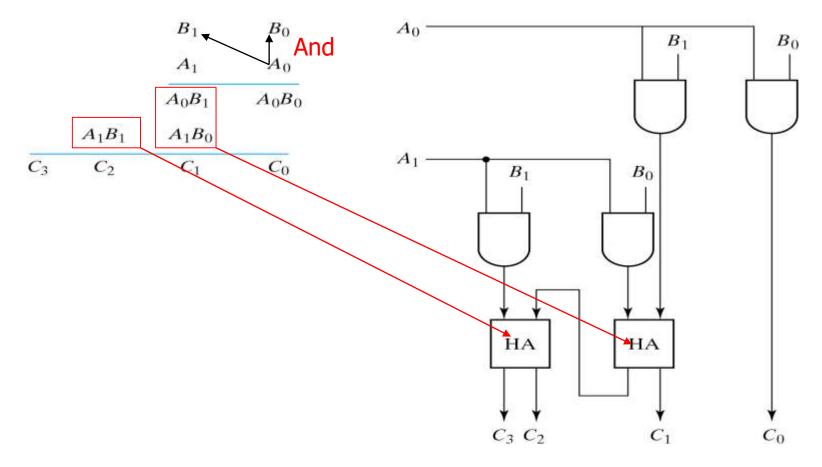

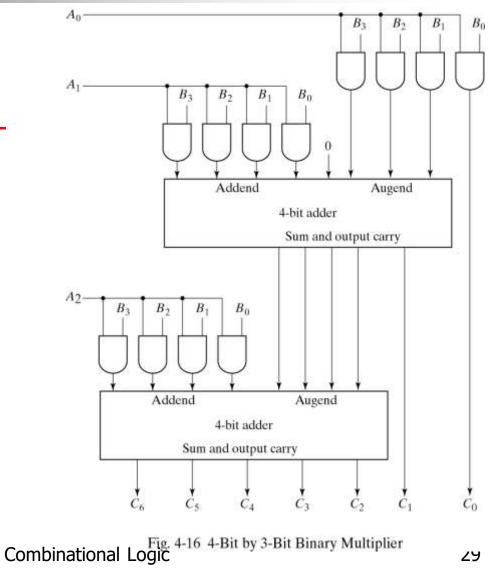

### **Binary multiplier**

Usually there are more bits in the partial products and it is necessary to use full adders to produce the sum of the partial products.

Fig. 4-15 2-Bit beambinational Multiplier

## 3-bit by 3-bit binary multiplier

- For J multiplier bits and K multiplicand bits we need (J X K) AND gates and (J – 1) K-bit adders to produce a product of J+K bits.

- K=3 and J=3, we need 12 AND gates and two 3-bit adders.

29

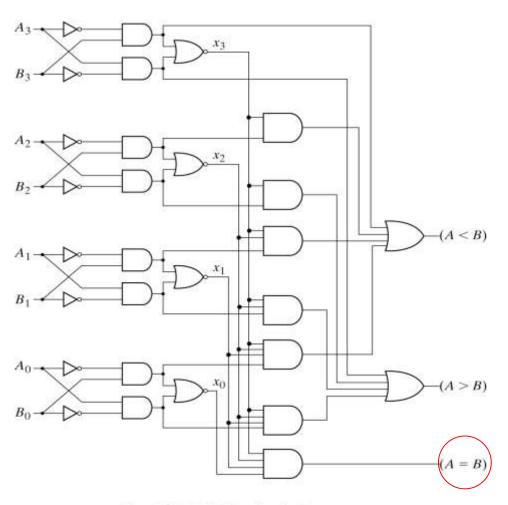

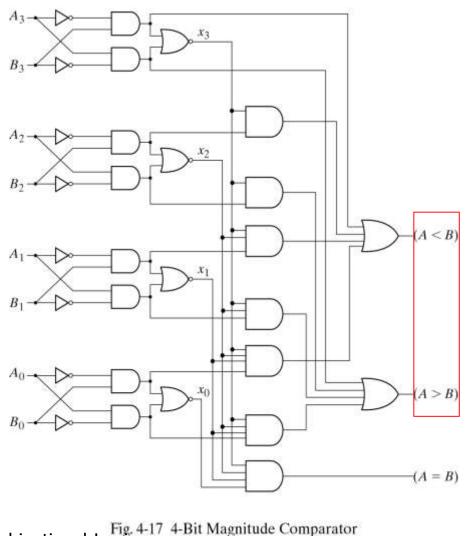

### Magnitude comparator

The equality relation of each pair of bits can be expressed logically with an exclusive-NOR function as:

$$A = A_3 A_2 A_1 A_0$$

;  $B = B_3 B_2 B_1 B_0$

$$x_i = A_i B_i + A_i' B_i'$$

for  $i = 0, 1, 2, 3$

$$(\mathsf{A} = \mathsf{B}) = \mathsf{x}_3 \mathsf{x}_2 \mathsf{x}_1 \mathsf{x}_0$$

Fig. 4-17 4-Bit Magnitude Comparator

### Magnitude comparator

- We inspect the relative magnitudes of pairs of MSB. If equal, we compare the next lower significant pair of digits until a pair of unequal digits is reached.

- If the corresponding digit of A is 1 and that of B is 0, we conclude that A>B.

```

(A > B) = A_{3}B'_{3} + x_{3}A_{2}B'_{2} + x_{3}x_{2}A_{1}B'_{1} + x_{3}x_{2}x_{1}A_{0}B'_{0}

(A < B) = A'_{3}B_{3} + x_{3}A'_{2}B_{2} + x_{3}x_{2}A'_{1}B_{1} + x_{3}x_{2}x_{1}A'_{0}B_{0}

II BTech(CSE) Combinational Logic

```

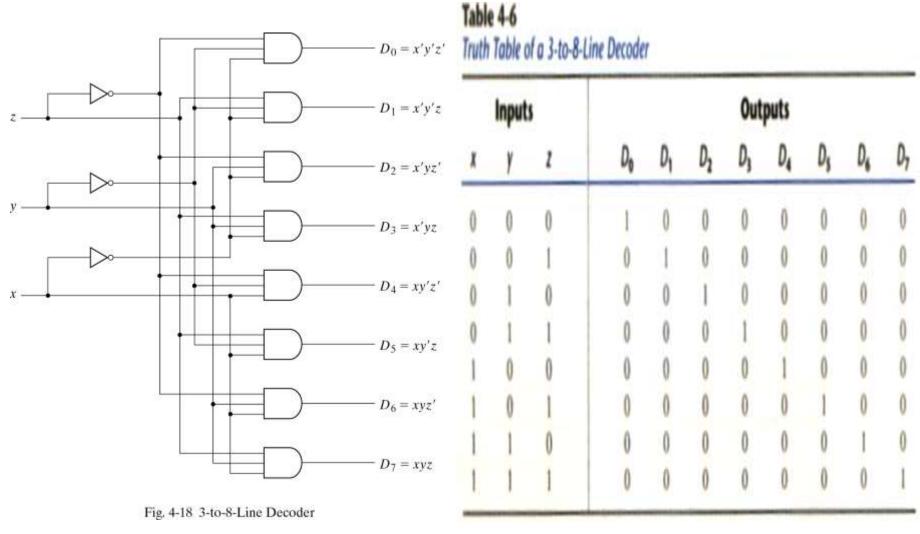

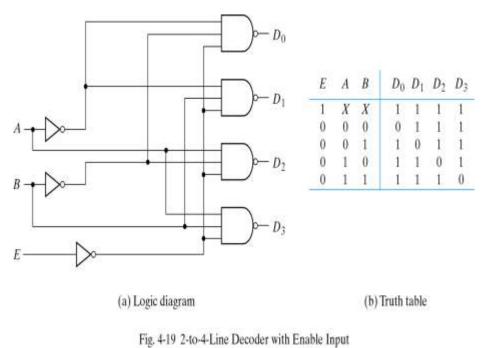

### Decoders

- The decoder is called n-to-m-line decoder, where  $m \le 2^n$  .

- the decoder is also used in conjunction with other code converters such as a BCD-to-seven\_segment decoder.

- 3-to-8 line decoder: For each possible input combination, there are seven outputs that are equal to 0 and only one that is equal to 1.

### Implementation and truth table

II BTech(CSE)

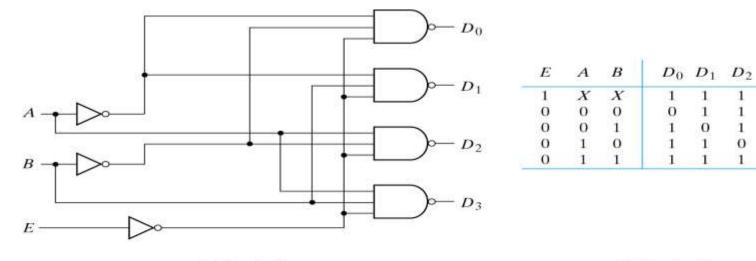

### Decoder with enable input

- Some decoders are constructed with NAND gates, it becomes more economical to generate the decoder minterms in their complemented form.

- As indicated by the truth table , only one output can be equal to 0 at any given time, all other outputs are equal to 1.

(a) Logic diagram

(b) Truth table

Fig. 4-19 2-to-4-Line Decoder with Enable Input Combinational Logic

$D_3$

0

1

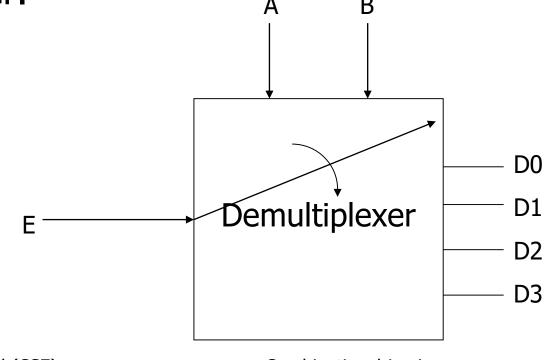

## Demultiplexer

- A decoder with an enable input is referred to as a decoder/demultiplexer.

- The truth table of demultiplexer is the same with decoder.

A B

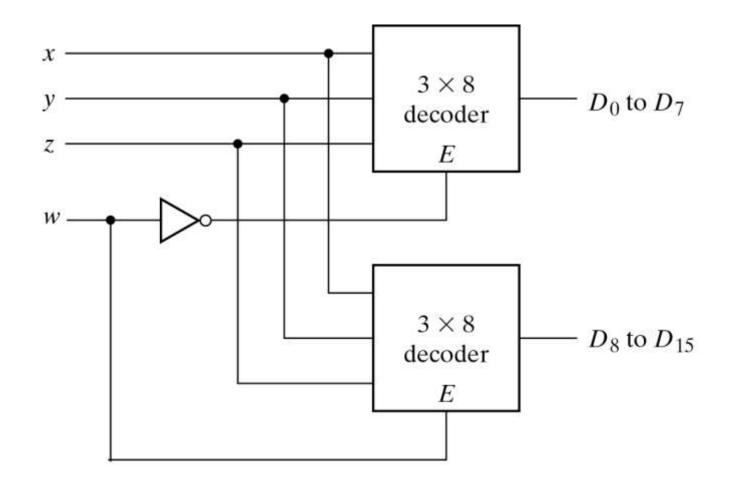

# 3-to-8 decoder with enable implement the 3-to-16 decoder

II Figh (ESE) 4 × 16 Decoder Constributional with Two 3 × 8 Decoders

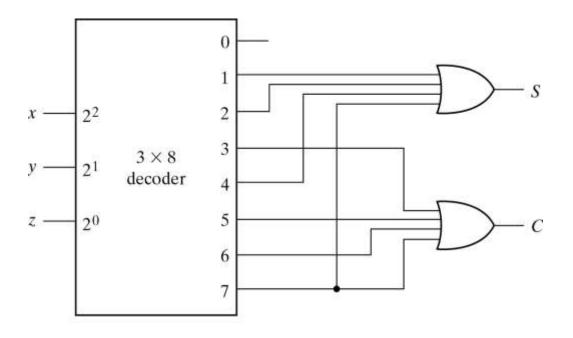

### Implementation of a Full Adder with a Decoder

From table 3-3, we obtain the functions for the combinational circuit in sum of minterms:

$S(x, y, z) = \Sigma(1, 2, 3, 7)$  $C(x, y, z) = \Sigma(3, 5, 6, 7)$

Fig. 4-21 Implementation of a Full Adder with a Decoder Combinational Logic

### 3-9. Encoders

- An encoder is the inverse operation of a decoder.

- We can derive the Boolean functions by table 3-7

$$z = D_1 + D_3 + D_5 + D_7$$

$$y = D_2 + D_3 + D_6 + D_7$$

$$x = D_3 + D_5 + D_6 + D_7$$

| Inputs |       |       |       |       |       |       | Out   | puts |   |   |

|--------|-------|-------|-------|-------|-------|-------|-------|------|---|---|

| $D_0$  | $D_1$ | $D_2$ | $D_3$ | $D_4$ | $D_5$ | $D_6$ | $D_7$ | x    | У | Z |

|        | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0    | 0 | C |

| )      | 1     | 0     | 0     | 0     | 0     | 0     | 0     | 0    | 0 | 1 |

| )      | 0     | 1     | 0     | 0     | 0     | 0     | 0     | 0    | 1 | ( |

| )      | 0     | 0     | 1     | 0     | 0     | 0     | 0     | 0    | 1 | 1 |

| )      | 0     | 0     | 0     | 1     | 0     | 0     | 0     | 1    | 0 | ( |

| )      | 0     | 0     | 0     | 0     | 1     | 0     | 0     | 1    | 0 | 1 |

| )      | 0     | 0     | 0     | 0     | 0     | 1     | 0     | 1    | 1 | ( |

| )      | 0     | 0     | 0     | 0     | 0     | 0     | 1     | 1    | 1 | 1 |

#### Table 4-7 Truth Table of Octal-to-Binary Encoder

### Priority encoder

- If two inputs are active simultaneously, the output produces an undefined combination. We can establish an input priority to ensure that only one input is encoded.

- Another ambiguity in the octal-to-binary encoder is that an output with all 0's is generated when all the inputs are 0; the output is the same as when D<sub>0</sub> is equal to 1.

- The discrepancy tables on Table 3-7 and Table 3-8 can resolve aforesaid condition by providing one more output to indicate that at least one input is equal to 1.

### Priority encoder

V=0→no valid inputs V=1→valid inputs

X's in output columns represent don't-care conditions X's in the input columns are useful for representing a truth table in condensed form. Instead of listing all 16 minterms of four variables.

### Table 4-8 Truth Table of a Priority Encoder

|    | Inp | uts            |                | ( | Outputs |   |  |  |

|----|-----|----------------|----------------|---|---------|---|--|--|

| Do | Dı  | D <sub>2</sub> | D <sub>3</sub> | x | y       | V |  |  |

| 0  | 0   | 0              | 0              | X | X       | 0 |  |  |

| 1  | 0   | 0              | 0              | 0 | 0       | 1 |  |  |

| X  | 1   | 0              | 0              | 0 | 1       | 1 |  |  |

| X  | X   | 1              | 0              | 1 | 0       | 1 |  |  |

| X  | X   | X              | 1              | 1 | 1       | 1 |  |  |

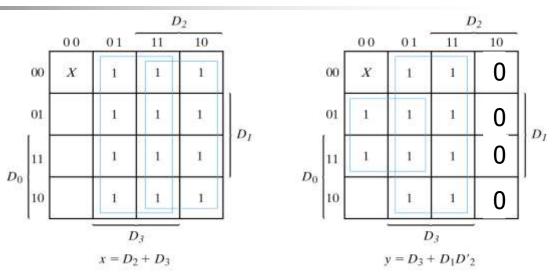

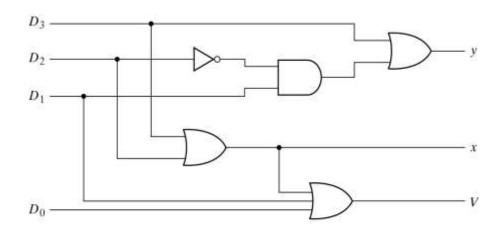

# 3-input priority encoder

- Implementation of table 3-8

- $x = D_2 + D_3$   $y = D_3 + D_1 D_2'$  $V = D_0 + D_1 + D_2 + D_3$

Fig. 4-22 Maps for a Priority Encoder

II BTech(CSE)

Combinationale Hogic Input Priority Encoder

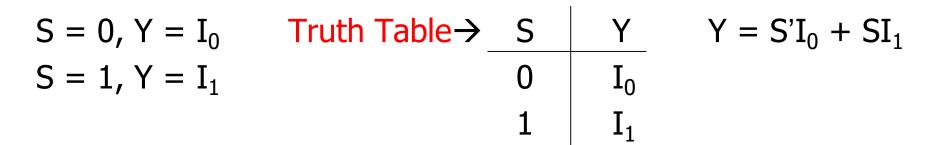

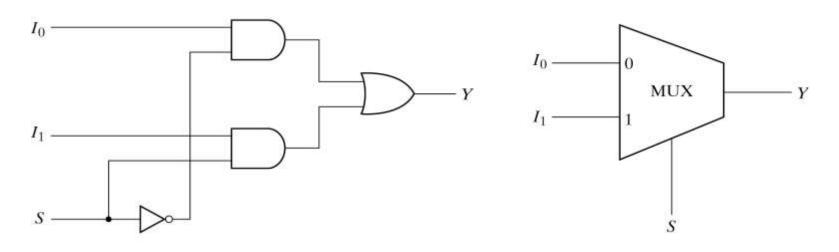

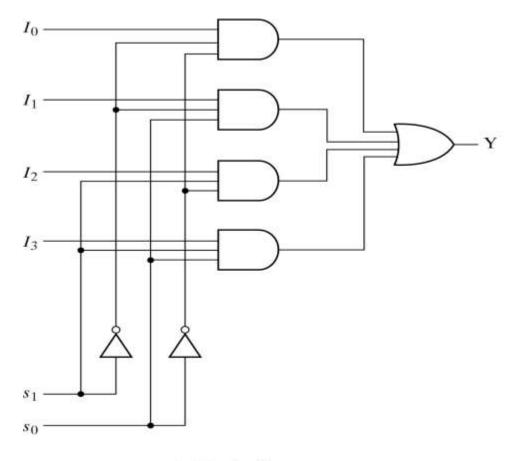

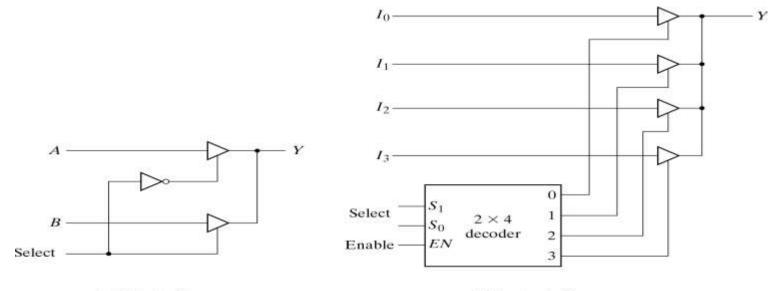

### **Multiplexers**

(a) Logic diagram

(b) Block diagram

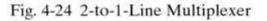

### 3-to-1 Line Multiplexer

|   | <i>s</i> <sub>1</sub> | 50 | Y     |

|---|-----------------------|----|-------|

| - | 0                     | 0  | $I_0$ |

|   | 0                     | 1  | $I_1$ |

|   | 1                     | 0  | $I_2$ |

|   | 1                     | 1  | 13    |

(b) Function table

(a) Logic diagram

Fig. 4-25 4-to-1-Line Multiplexer Combinational Logic

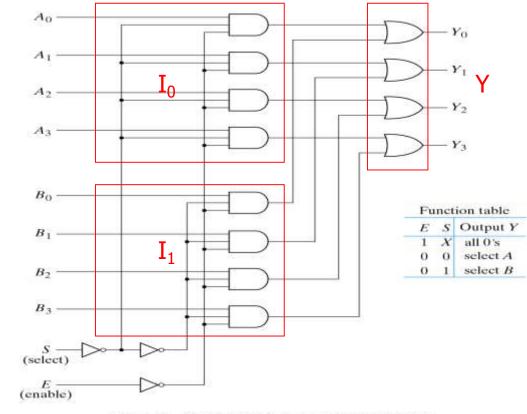

### Quadruple 2-to-1 Line Multiplexer

Multiplexer circuits can be combined with common selection inputs to provide multiple-bit selection logic. Compare with Fig3-23.

II BTech(CSE)

Fig. 4-26 Quadruple 2-to-1-Line Multiplexer Combinational Logic

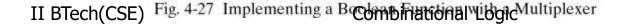

### **Boolean function implementation**

A more efficient method for implementing a Boolean function of n variables with a multiplexer that has n-1 selection inputs.

$F(y, y, z) = \Sigma(1, 2, 6, 7)$

# 3-input function with a multiplexer

$F(A, B, C, D) = \Sigma(1, 3, 3, 11, 12, 13, 13, 15)$

II BTech(CSE) Fig. 4-28 Implementing a Combination with a Multiplexer

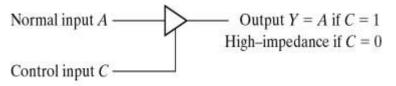

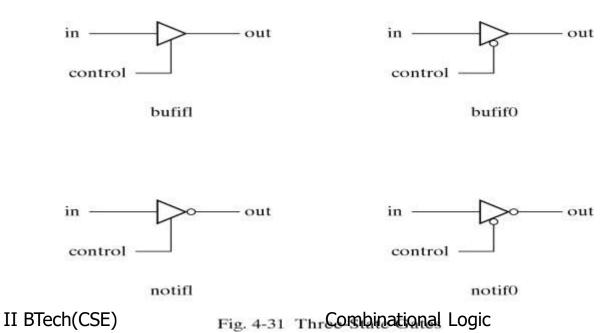

### **Three-State Gates**

A multiplexer can be constructed with three-state gates.

Fig. 4-29 Graphic Symbol for a Three-State Buffer

(a) 2-to-1- line mux

(b) 4 - to - 1 line mux

Fig. 4-30 Multiplexers with Three-State Gates Combinational Logic

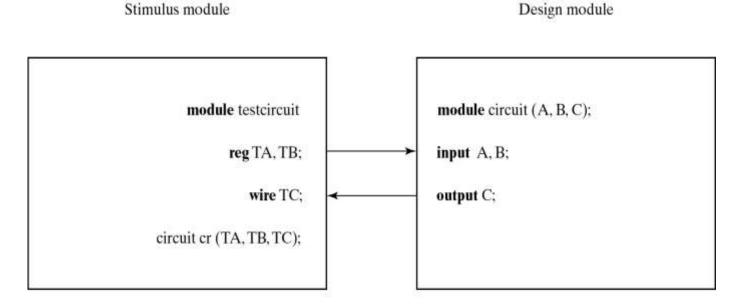

### HDL for combinational circuits

- A module can be described in any one of the following modeling techniques:

- 1. Gate-level modeling using instantiation of primitive gates and user-defined modules.

- 2. Dataflow modeling using continuous assignment statements with keyword assign.

- 3. Behavioral modeling using procedural assignment statements with keyword always.

### **Gate-level Modeling**

- A circuit is specified by its logic gates and their interconnection.

- Verilog recognizes 12 basic gates as predefined primitives.

- The logic values of each gate may be 1, 0, x(unknown), z(highimpedance).

| and | 0 | 1 | х | z | or  | 0   | 1  | х   | Z   |

|-----|---|---|---|---|-----|-----|----|-----|-----|

| 0   | 0 | 0 | 0 | 0 | 0   | 0   | 1  | x   | x   |

| 1   | 0 | 1 | х | х | 1   | 1   | 1  | 1   | 1   |

| х   | 0 | х | х | x | x   | x   | 1  | х   | x   |

| z   | 0 | x | x | x | Z   | x   | 1  | х   | x   |

| xor | 0 | 1 | x | Z | not | inp | ut | out | put |

| 0   | 0 | 1 | х | x |     | 0   |    | 1   |     |

| 1   | 1 | 0 | x | x |     | 1   |    | 0   |     |

| x   | x | х | x | x |     | x   |    | x   |     |

|     |   | x | x |   |     | Z   |    | x   |     |

Table 4-9 Truth Table for Predefined Primitive Gates

II BTech(CSE)

### Gate-level description on Verilog code

### The wire declaration is for internal connections.

### HDL Example 4-1

```

//Gate-level description of a 2-to-4-line decoder

//Figure 4-19

module decoder gl (A, B, E, D);

input A, B, E;

output [0:3]D;

wire Anot, Bnot, Enot;

not

n1

(Anot, A),

n2

(Bnot, B),

n3

(Enot, E);

nand

(D[0], Anot, Bnot, Enot),

n4

(D[1], Anot, B, Enot),

n5

(D[2], A, Bnot, Enot),

n6

n7

(D[3], A, B, Enot);

endmodule

```

II BTech(CSE)

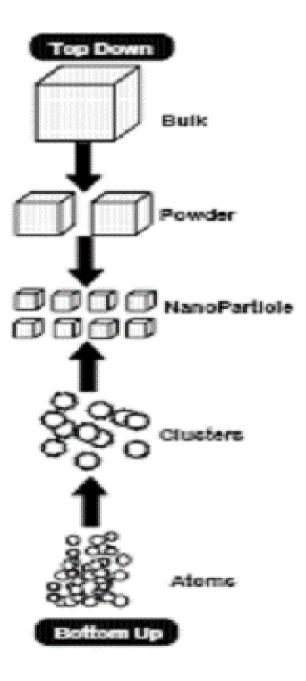

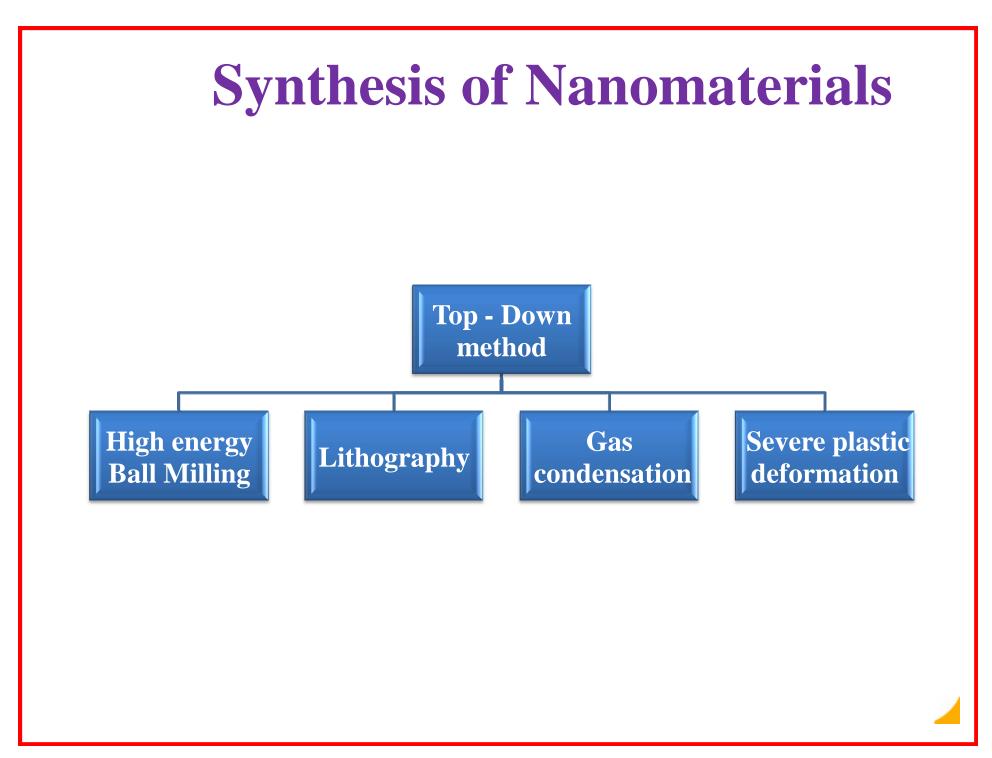

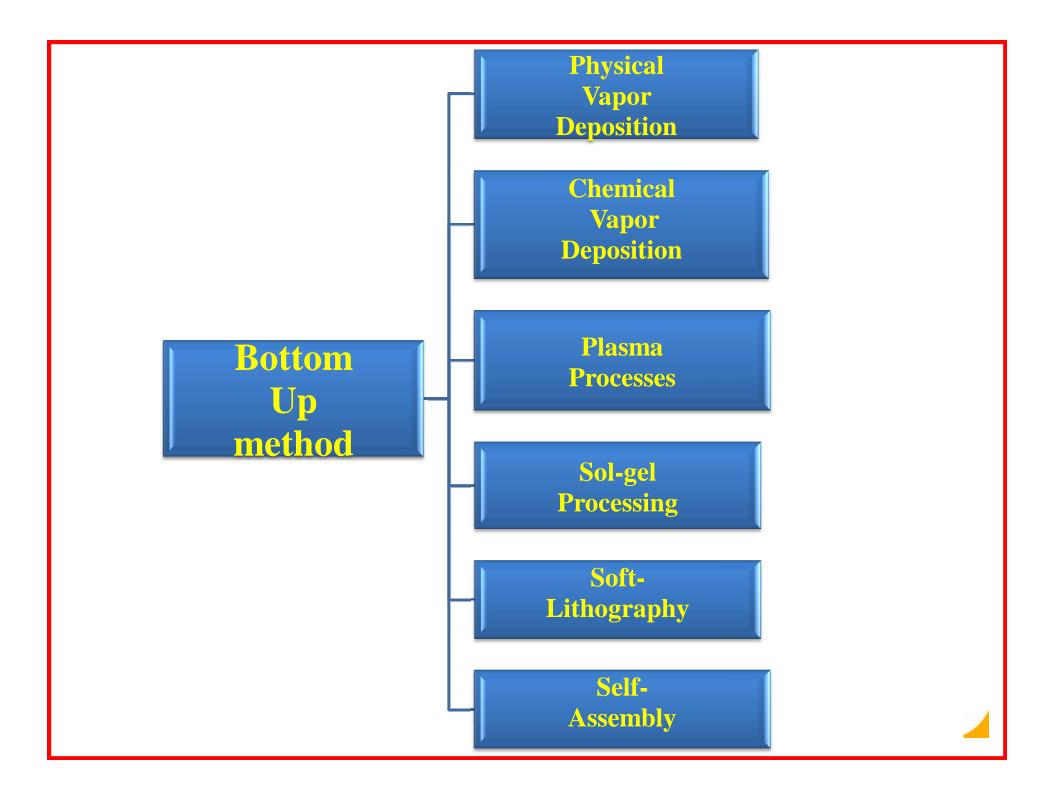

# Design methodologies

- There are two basic types of design methodologies: topdown and bottom-up.

- Top-down: the top-level block is defined and then the subblocks necessary to build the top-level block are identified.(Fig.3-9 binary adder)

- Bottom-up: the building blocks are first identified and then combined to build the top-level block.(Example 3-2 3-bit adder)

## A bottom-up hierarchical description

#### HDL Example 4-2

```

//Gate-level hierarchical description of 4-bit adder

// Description of half adder (see Fig 4-5b)

module halfadder (S,C,x,y);

input x,y;

output S,C;

//Instantiate primitive gates

xor (S, x, y);

and (C, x, y);

Combinational Logic

II BTech(CSE)

```

# Full-adder

```

//Description of full adder (see Fig 4-8)

module fulladder (S,C,x,y,z);

input x,y,z;

output S,C;

wire S1, D1, D2; //Outputs of first XOR and two AND gates

//Instantiate the halfadder

halfadder HA1 (S1, D1, x, y),

HA2 (S, D2, S1, z);

or g1(C, D2, D1);

Combinational Logic

```

# 3-bit adder

```

//Description of 4-bit adder (see Fig 4-9)

module _4bit_adder (S,C4,A,B,C0);

input [3:0] A,B;

input CO;

output [3:0] S;

output C4;

wire C1, C2, C3; //Intermediate carries

//Instantiate the fulladder

fulladder FA0 (S[0],C1,A[0],B[0],C0),

FA1 (S[1],C2,A[1],B[1],C1),

FA2 (S[2],C3,A[2],B[2],C2),

FA3 (S[3],C4,A[3],B[3],C3);

```

Combinational Logic

# Three state gates

Gates statement: gate name(output, input, control) >> bufif1(OUT, A, control);

- A = OUT when control = 1, OUT = z when control = 0; >> notif0(Y, B, enable);

- Y = B' when enable = 0, Y = z when enable = 1;

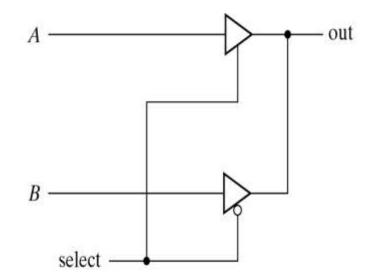

# 2-to-1 multiplexer

HDL uses the keyword tri to indicate that the output has multiple drivers.

```

module muxtri (A, B, select, OUT);

input A,B,select;

output OUT;

tri OUT;

bufif1 (OUT,A,select);

bufif0 (OUT,B,select);

endmodule

```

Fig. 4-32 2-to-1-Line Multiplexer with Three-State Buffers

# Dataflow modeling

It uses a number of operators that act on operands to produce desired results. Verilog HDL provides about 30 operator types.

Table 3-10

| Operation               |                                                                                                                                                                |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| binary addition         |                                                                                                                                                                |

| binary subtraction      |                                                                                                                                                                |

| bit-wise AND            |                                                                                                                                                                |

| bit-wise OR             |                                                                                                                                                                |